# Inductance-Independent Discontinuous Current Mode Control with Minimized Inductor for Power Converters

A thesis submitted to

#### NAGAOKA UNIVERSITY OF TECHNOLOGY

for the degree of

DOCTOR OF ENGINEERING

presented by

#### HOAI NAM LE

accepted on the recommendation of

Prof. Dr. Jun-ichi Itoh

2018

Nagaoka University of Technology Power Electronics Laboratory <u>http://itohserver01.nagaokaut.ac.jp/itohlab/en/index.html</u> © 2018 by Hoai Nam Le

## Acknowledgements

First and foremost, I would like to thank Prof. Jun-ichi Itoh for giving me the opportunity to be part of the excellent working environment he has built up at the Power Electronics Laboratory of the Nagaoka University of Technology. He has supported and encouraged me in research over these years. He has also provided me many wonderful opportunities to participate in national and international conferences, and internship program. I also thank Associate Prof. Takanori Isobe, who is with Tsukuba University, for his interests in this work. I sincerely appreciate that he found time to travel to Nagaoka to take part in my PhD defense as a co-examiner.

I would like to express my gratitude and appreciation to Prof. Seiji Kondo, Prof. Kiyoshi Ohishi, Associate Prof. Toshimasa Miyazaki, Associate Prof. Hitoshi Haga, Assistant Prof. Yuki Yokokura, and Assistant Prof. Keisuke Kusaka, who are with the Power Laboratory from Nagaoka University of Technology, and Assistant Prof. Koji Orikawa, who is with Hokkaido University. My thanks also go to Dr. Hiroki Takahashi and Dr. Daisuke Sato, who are with Yaskawa Electric Corporation and Nagaoka Motor Development Corporation, for teaching and supporting me.

Further, I warmly thank everybody else in the Power Laboratory, in particular Dr. Hiroki Watanabe, Mr. Hayato Higa and Mrs. Nagisa Ohnuma for their motivating and helpful discussions as well as for the good times we had in the Power Lab.

My study and research in Nagaoka University of Technology has been a wonderful experience. I was supported by the Japan student services organization, the KDDI scholarship foundation, and the Sato Yo international scholarship foundation. Further, this research would not have been possible without the financial supports from Mitsubishi Electric Corporation. Finally, I would like to express my thanks and loves to my family, for their moral support, patience and encouragement. Their love is the key to the successes in my life.

Nagaoka, November 2018 Hoai Nam Le

# Table of Contents

| Title page      | ······i      |

|-----------------|--------------|

| Acknowledgen    | nentsiii     |

| Table of Conter | nts ······ v |

| List of Figures | X            |

| List of Tables  | XV           |

#### Chapter 1

#### Introduction

| 1.1  | Background             | 1 |

|------|------------------------|---|

| 1.2  | Research Objectives    | 8 |

| 1.3  | Thesis Outline ······1 | 5 |

| Bibl | ography ······1        | 9 |

#### Chapter 2

### Inductance-Independent Control for Continuous and Discontinuous Current Mode

| 2.1 Introduction ······ | •2 | 2 | 5 |

|-------------------------|----|---|---|

|-------------------------|----|---|---|

| 2.2          | Inductor | Minimization with CCM&DCM Control Method 27                       |

|--------------|----------|-------------------------------------------------------------------|

| 2.3          | Overview | w of Continuous and Discontinuous Current Mode Control            |

| 2.4          | Convent  | ional Discontinuous Current Mode Control                          |

|              | 2.4.1    | DCM Feedforward Control                                           |

|              | 2.4.2    | DCM Feedback Control45                                            |

|              | 2.4.3    | Problems of Inductance-Dependent Control Systems                  |

|              | 2.4.4    | Comparison of Conventional Control Methods                        |

| 2.5          | Proposed | d Inductance-Independent Control for Continuous and Discontinuous |

| Current Mode |          |                                                                   |

|              | 2.5.1    | Inductance-Independent Control for Continuous and Discontinuous   |

|              |          | Current Mode with Duty at Previous Calculation Period56           |

|              | 2.5.2    | Beneficial Position of Proposed Method59                          |

| 2.6          | Conclus  | ion62                                                             |

| Bibl         | iography | 64                                                                |

#### **Control for Discontinuous Current Mode in Boost Converter**

| 3.1 | Introduc                                            | ction69                                                               |  |  |

|-----|-----------------------------------------------------|-----------------------------------------------------------------------|--|--|

| 3.2 | Problem                                             | Problems of Conventional Discontinuous Current Mode Control Methods71 |  |  |

| 3.3 | PI Controller Design for Continuous Current Mode78  |                                                                       |  |  |

| 3.4 | Current                                             | Current Control for Discontinuous Current Mode                        |  |  |

|     | 3.4.1                                               | Circuit Model Derivation ······83                                     |  |  |

|     | 3.4.2                                               | Nonlinearity Compensation with Duty Ratio at Previous Calculation     |  |  |

|     |                                                     | Period                                                                |  |  |

| 3.5 | Synchronous Switching in Discontinuous Current Mode |                                                                       |  |  |

| 3.6 | Experin                                             | nental Results                                                        |  |  |

|     | 3.6.1                                               | Frequency Analysis, Current Step Response and Load Transient          |  |  |

|              | Response ······95                                                |

|--------------|------------------------------------------------------------------|

| 3.6.2        | Discontinuous-Current-Mode Synchronous Switching Operation       |

|              | Waveforms, and Comparison of Efficiency and Computation Time 104 |

| 3.7 Conclu   | sion 109                                                         |

| Bibliography |                                                                  |

| Cur   | rent Co  | ntrol for Discontinuous and Continuous Current Mode in           |

|-------|----------|------------------------------------------------------------------|

| Sing  | le-Phase | Grid-Tied Inverter                                               |

| 4.1   | Introduc | tion 113                                                         |

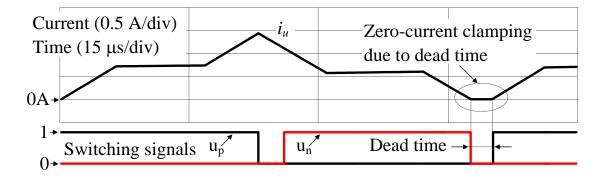

| 4.2   | Zero-Cu  | rrent Clamping Phenomenon                                        |

| 4.3   | Current  | Control for Discontinuous Current Mode and Continuous Current    |

|       | Mode     |                                                                  |

|       | 4.3.1    | Circuit Model Derivation 124                                     |

|       | 4.3.2    | Nonlinearity Compensation with Duty at Previous Calculation      |

|       |          | Period 129                                                       |

|       | 4.3.3    | Current Mode Determination                                       |

| 4.4   | Experim  | ental Results                                                    |

|       | 4.4.1    | Construction and Assembly                                        |

|       | 4.4.2    | Operation Verification                                           |

|       | 4.4.3    | Comparison of Efficiency, Inductor Material Cost and Computation |

|       |          | Time165                                                          |

| 4.5   | Conclus  | ion 173                                                          |

| Bibli | iography |                                                                  |

#### Chapter 5

Control for Discontinuous Current Mode in Three-Phase Grid-Tied Inverter

| 5.1  | Introduc                                           | tion                                                       |  |

|------|----------------------------------------------------|------------------------------------------------------------|--|

| 5.2  | 5.2 Current Control for Discontinuous Current Mode |                                                            |  |

|      | 5.2.1                                              | Zero Crossing Distortion 184                               |  |

|      | 5.2.2                                              | Circuit Model Derivation 189                               |  |

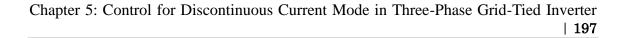

|      | 5.2.3                                              | Discontinuous Current Mode Control System                  |  |

| 5.3  | Simulati                                           | on Results ······ 200                                      |  |

| 5.4  | Experim                                            | iental Results                                             |  |

|      | 5.4.1                                              | Operation Verification                                     |  |

|      | 5.4.2                                              | Efficiency Comparison between Asynchronous and Synchronous |  |

|      |                                                    | Switching                                                  |  |

| 5.5  | Conclus                                            | ion                                                        |  |

| Bibl | iography                                           |                                                            |  |

#### Hybrid Discontinuous Current Mode

| 6.1 | Introduc | tion                                                           |

|-----|----------|----------------------------------------------------------------|

| 6.2 | Hybrid ( | Current Mode between Discontinuous Current Mode and Triangular |

|     | Current  | Mode                                                           |

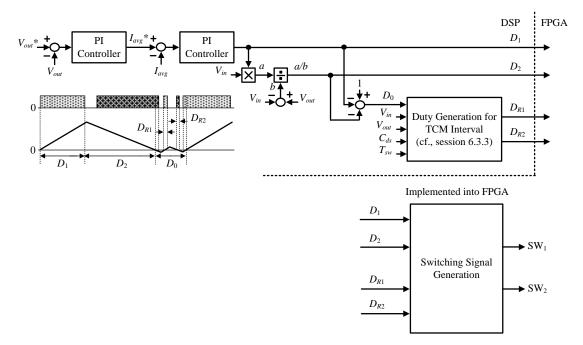

| 6.3 | Operatio | on of Hybrid Discontinuous Current Mode                        |

|     | 6.3.1    | Converter Design ······ 233                                    |

|     | 6.3.2    | Control System ······ 238                                      |

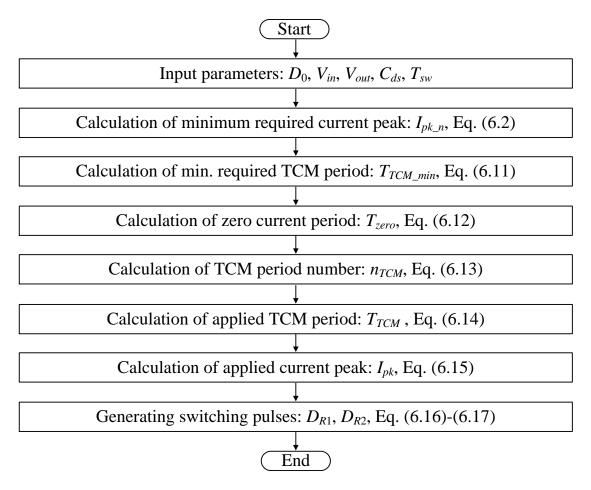

|     | 6.3.3    | Duty Generation for Triangular Current Mode Interval           |

| 6.4 | Experim  | ental Results                                                  |

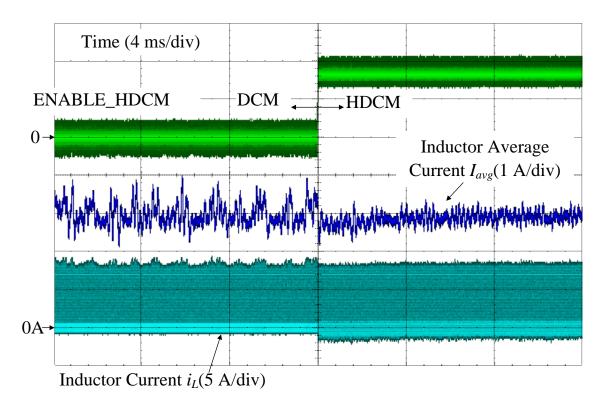

|     | 6.4.1    | Operation Verification                                         |

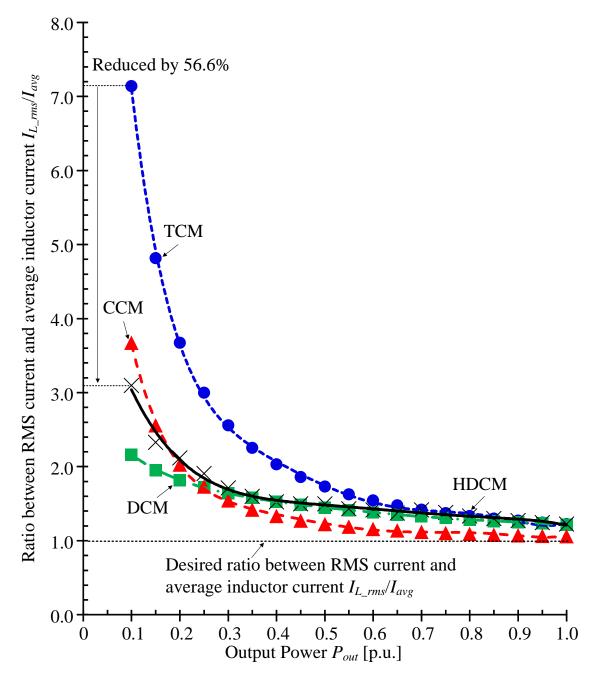

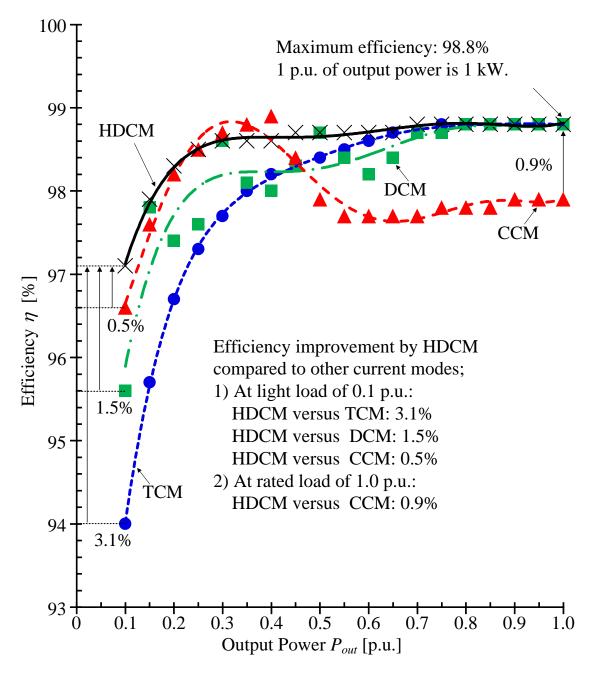

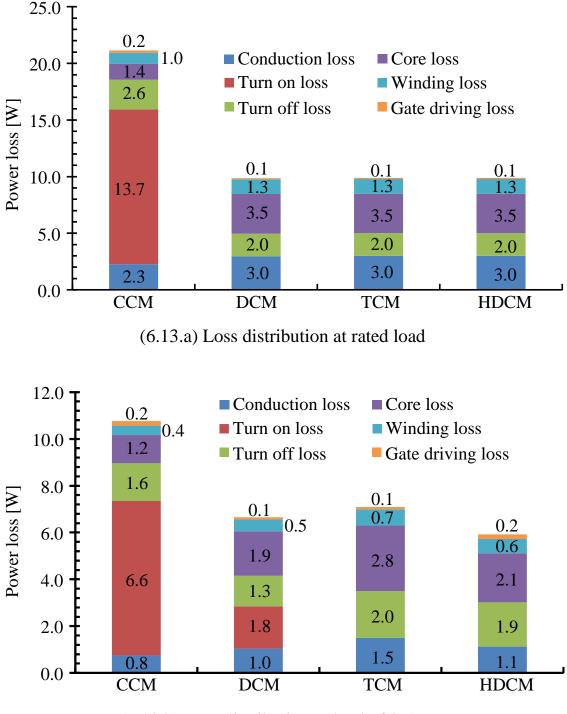

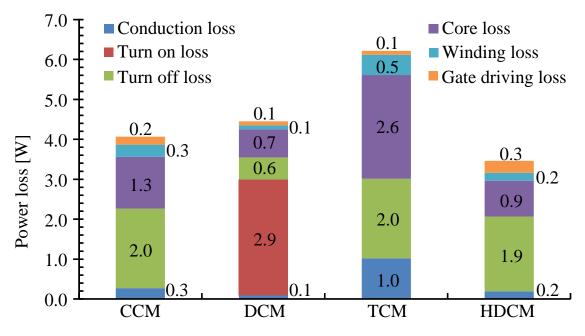

|     | 6.4.2    | Comparisons of Root-Mean-Square Current and Efficiency 257     |

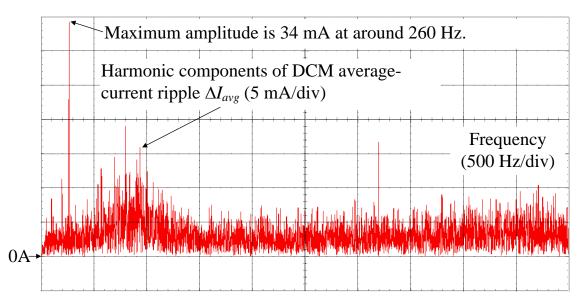

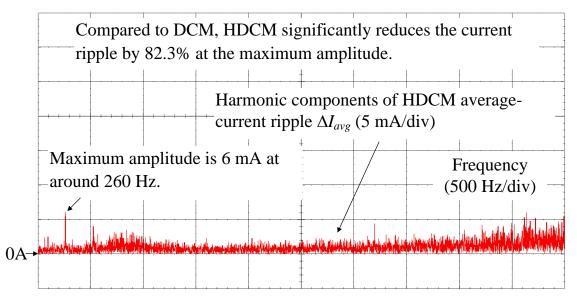

|     | 6.4.3    | Average Current Ripple Reduction and Output Voltage Regulation |

|     |          |                                                                |

| 6.5   | Conclusio | on ····· 2 | 270 |

|-------|-----------|------------|-----|

| Bibli | ography   |            | 273 |

### Conclusion

| 7.1 | Discussi     | ion 275                                                     |  |

|-----|--------------|-------------------------------------------------------------|--|

| 7.2 | Future Works |                                                             |  |

|     | 7.2.1        | Island Mode Operation                                       |  |

|     | 7.2.2        | CCM/DCM Feedback Current Control for Three-phase Converters |  |

|     |              |                                                             |  |

|     |              |                                                             |  |

| List of Achievements ······ 2 | 284 |

|-------------------------------|-----|

|-------------------------------|-----|

# List of Figures

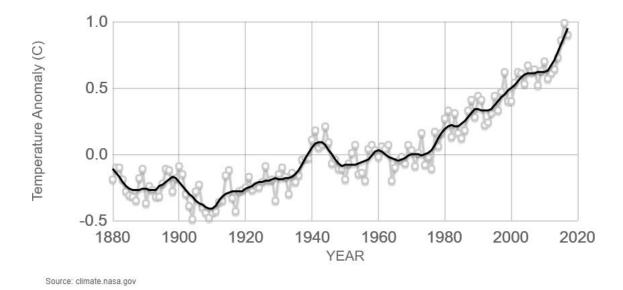

| Figure 1.1 | Temperature anomaly from 1880 to 2017                                 |

|------------|-----------------------------------------------------------------------|

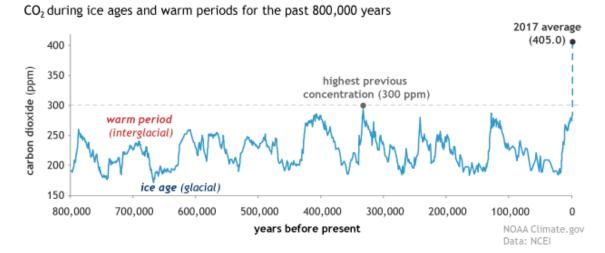

| Figure 1.2 | Atmospheric carbon dioxide concentrations in parts per                |

| millio     | on (ppm) for the past 800,000 years                                   |

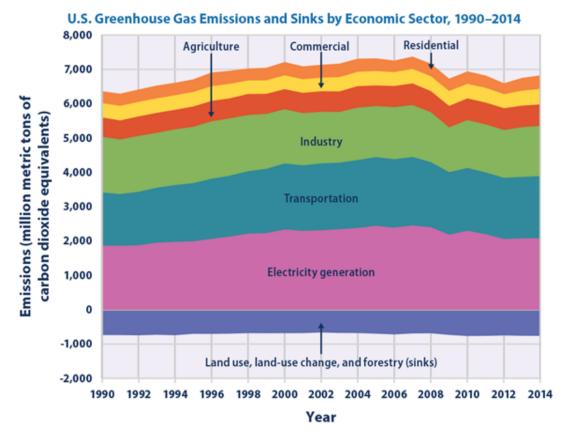

| Figure 1.3 | U.S. greenhouse gas emissions and sinks by economic sector            |

| from       | 1990 to 2014                                                          |

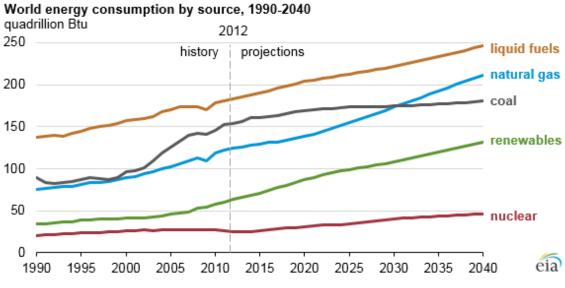

| Figure 1.4 | World energy consumption by source from 1990 to 2040 5                |

| Figure 1.5 | Electricity generation system employing renewable energy              |

| sourc      | es ······ 7                                                           |

| Figure 1.6 | Breakdown of the solar power systems7                                 |

| Figure 1.7 |                                                                       |

| with       | power rating of 1 kW······9                                           |

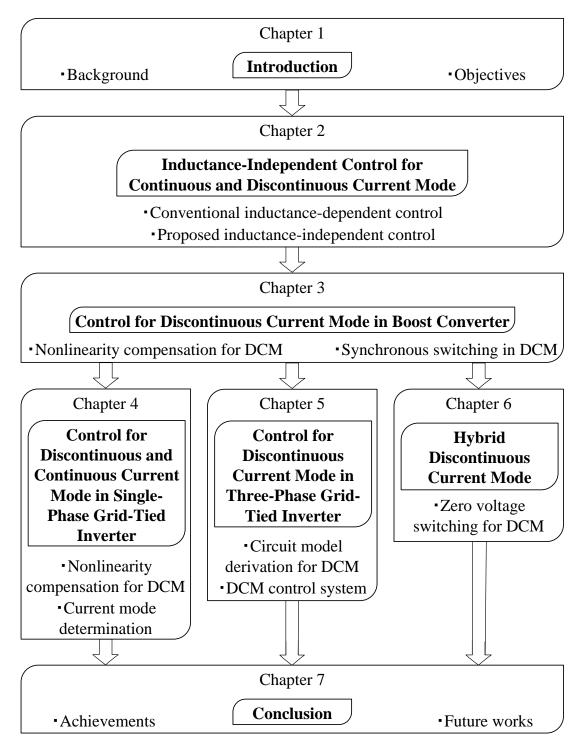

| Figure 1.8 | Outline of the thesis 16                                              |

| Chapter 2  |                                                                       |

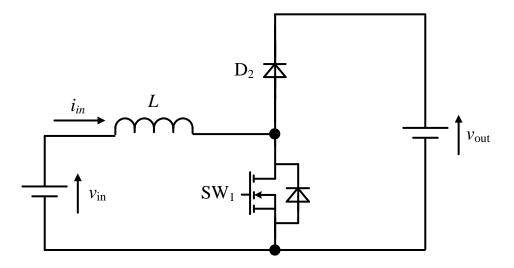

| Figure 2.1 | Typocal boost converter                                               |

| Figure 2.2 | Relationship among current ripple, inductor volume and                |

| heatsi     | nk volume······ 31                                                    |

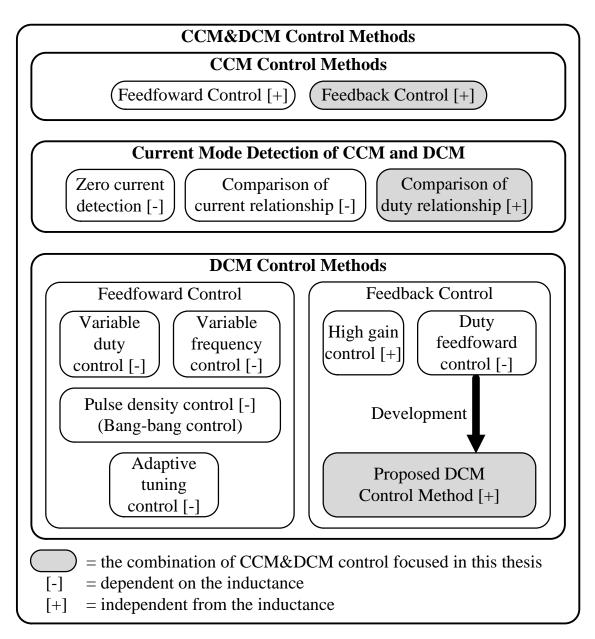

| Figure 2.3 | Classification of CCM&DCM control methods                             |

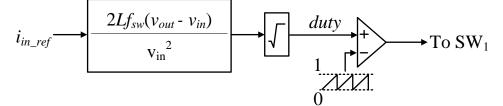

| Figure 2.4 | Variable duty control system for DCM in DC/DC converter               |

|            |                                                                       |

| Figure 2.5 | Variable frequency control system for DCM in DC/AC                    |

| conve      | erter                                                                 |

| -          | Pulse density control system for DCM in DC/DC converter $\cdot \cdot$ |

|            |                                                                       |

| Figure 2.7 | Adaptive tuning control system for DCM in DC/DC                       |

| conver      | rter 43                                                      |

|-------------|--------------------------------------------------------------|

| Figure 2.8  | Duty feedforward control for boost converter operation in    |

| both C      | CCM and DCM                                                  |

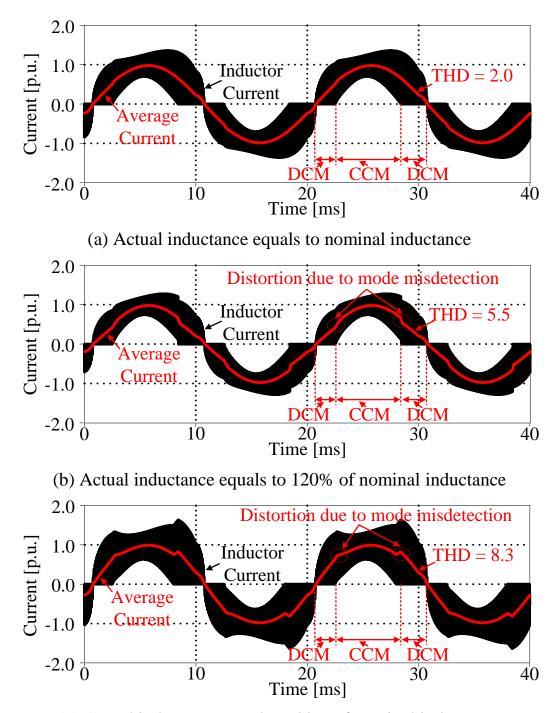

| Figure 2.9  | Single-phase inverter current waveform operating under       |

| CCM         | and DCM with the duty feedforward control (cf. Chapter 2.4.2 |

| of (2))     | and several different cases of the inductance error 51       |

| Figure 2.10 | Proposed inductance-independent control for inverter         |

| operat      | ing in CCM&DCM······ 57                                      |

| Figure 2.11 | Beneficial position of proposed method compared to           |

| conver      | ntional methods 59                                           |

| -           |                                                                |

|-------------|----------------------------------------------------------------|

| Figure 3.1  | Circuit diagram of typical boost converter 73                  |

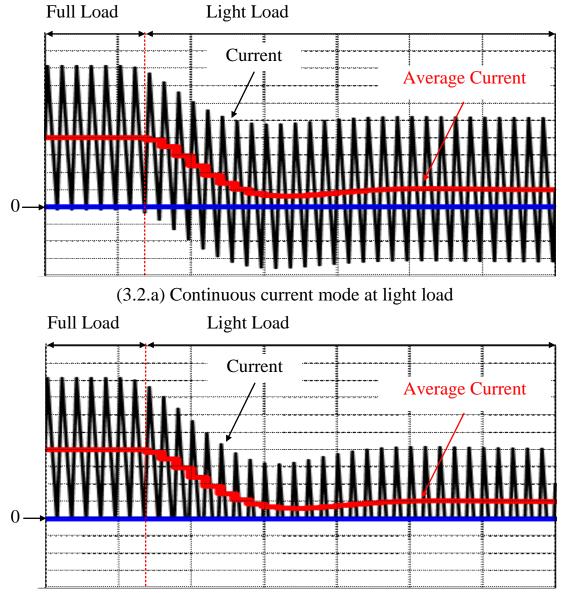

| Figure 3.2  | Inductor current waveform of CCM and DCM when the              |

| inducta     | ance is minimized at given switching frequency                 |

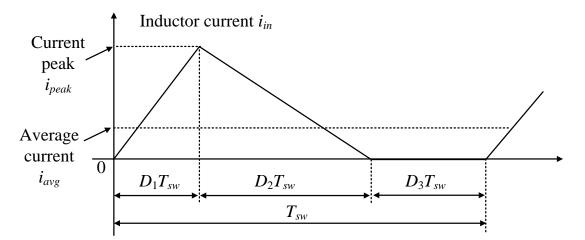

| Figure 3.3  | Inductor current waveform in DCM······ 78                      |

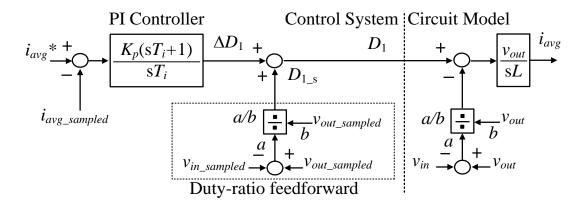

| Figure 3.4  | Current control system for CCM 81                              |

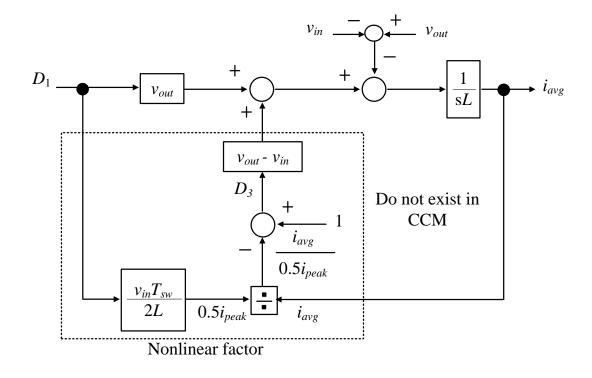

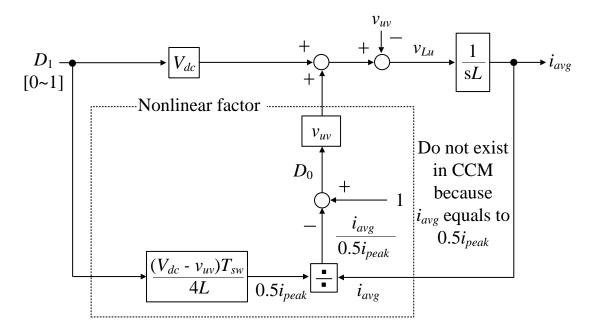

| Figure 3.5  | Circuit model of boost converter operated in DCM 84            |

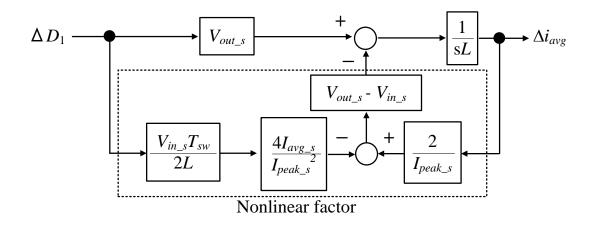

| Figure 3.6  | Linearized circuit model 85                                    |

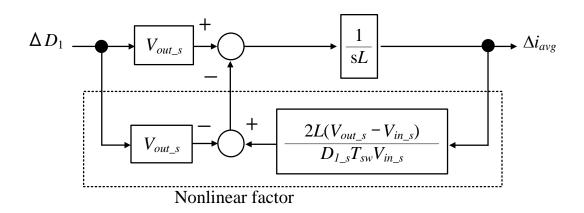

| Figure 3.7  | Simplified and linearized circuit model······ 86               |

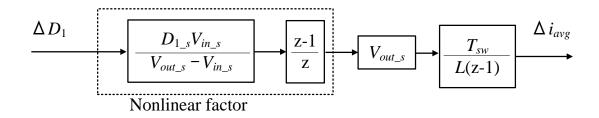

| Figure 3.8  | Discretized circuit model                                      |

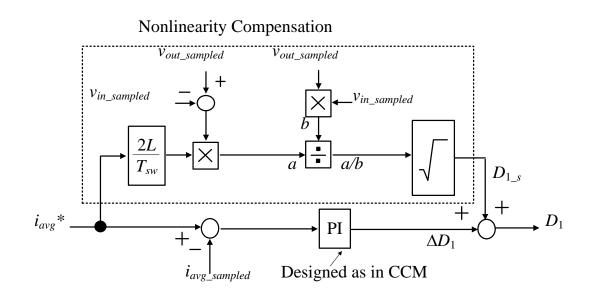

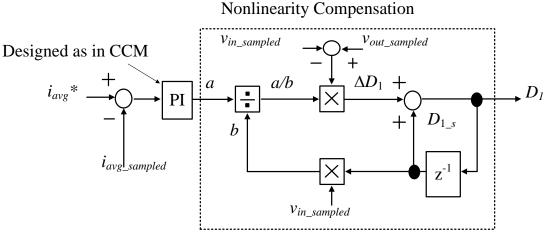

| Figure 3.9  | Conventional and proposed DCM nonlinearity compensation        |

| •••••       |                                                                |

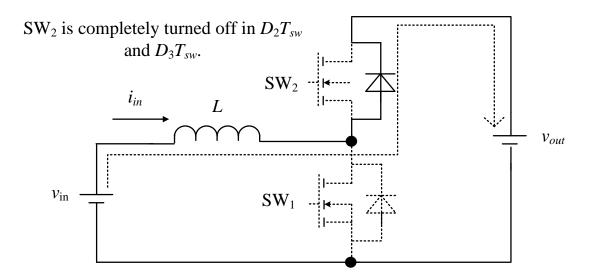

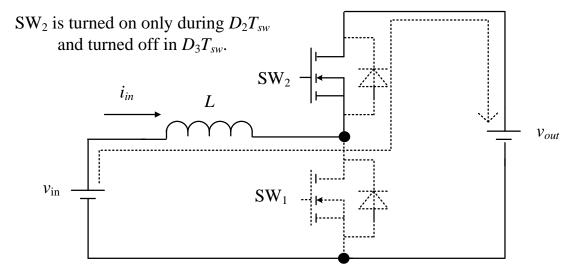

| Figure 3.10 | Asynchronous switching and synchronous switching in DCM        |

| •••••       |                                                                |

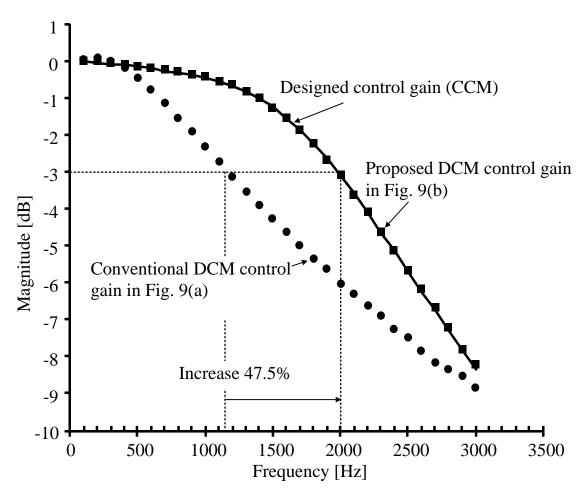

| -           | Frequency characteristics of conventional and proposed         |

| DCM of      | current feedback control                                       |

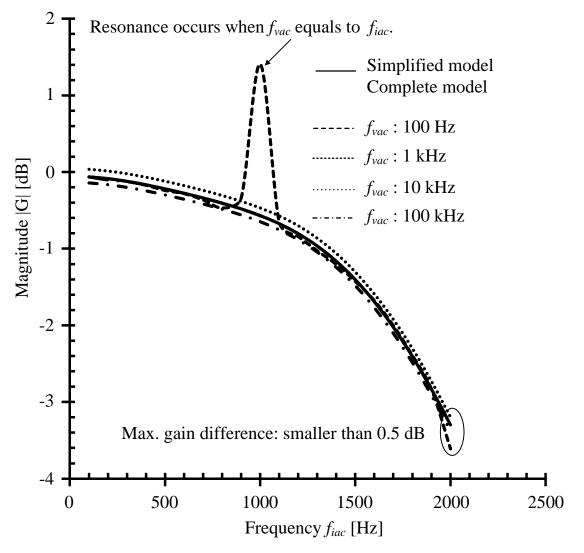

| Figure 3.12 | Frequency characteristics of closed-loop transfer function     |

| betwee      | en average inductor current and its reference using simplified |

|             | and complete model that includes also output voltage           |

| dynam       | ic 99                                                          |

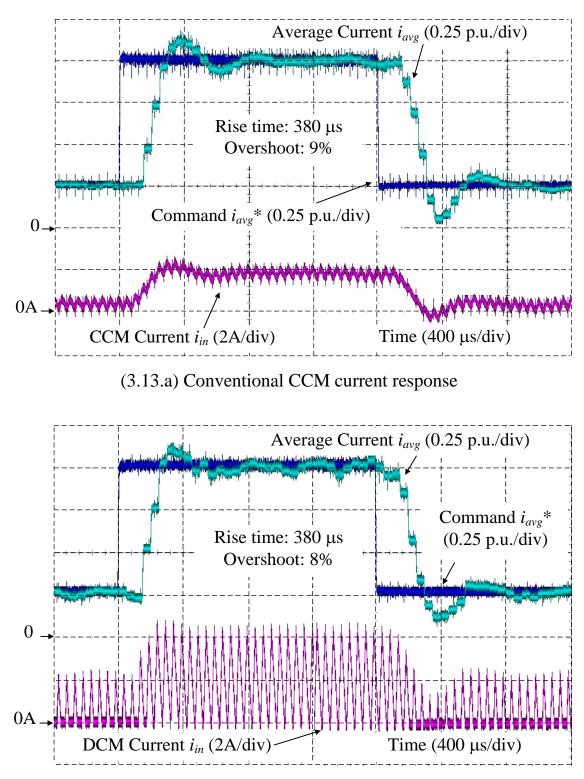

| •           | Current step response by input current control with 2-kHz      |

| cutoff      | frequency in CCM and DCM                                       |

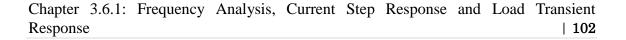

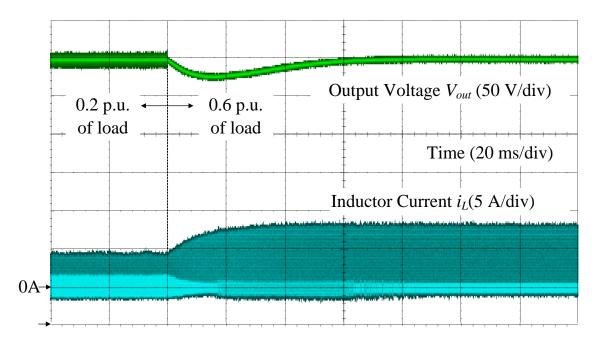

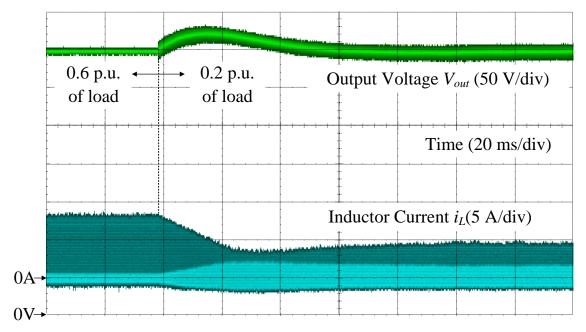

| -           | Load transient response by output voltage control with         |

| 0.2-kH      | z cutoff frequency                                             |

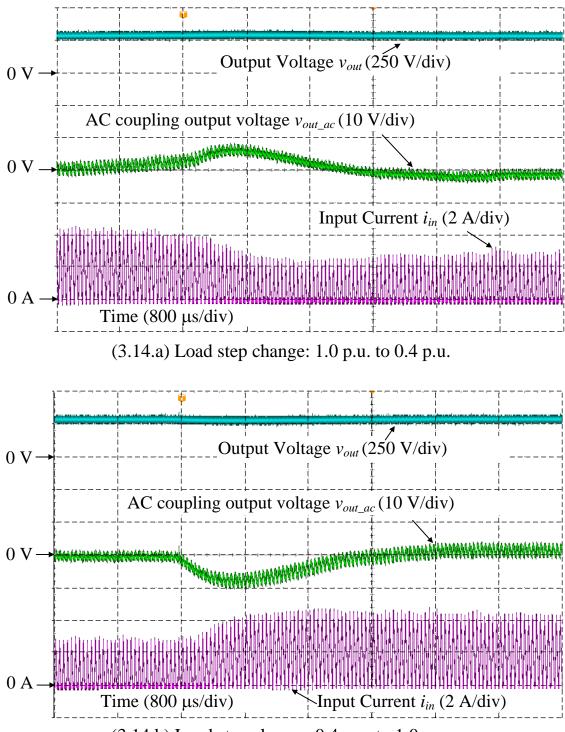

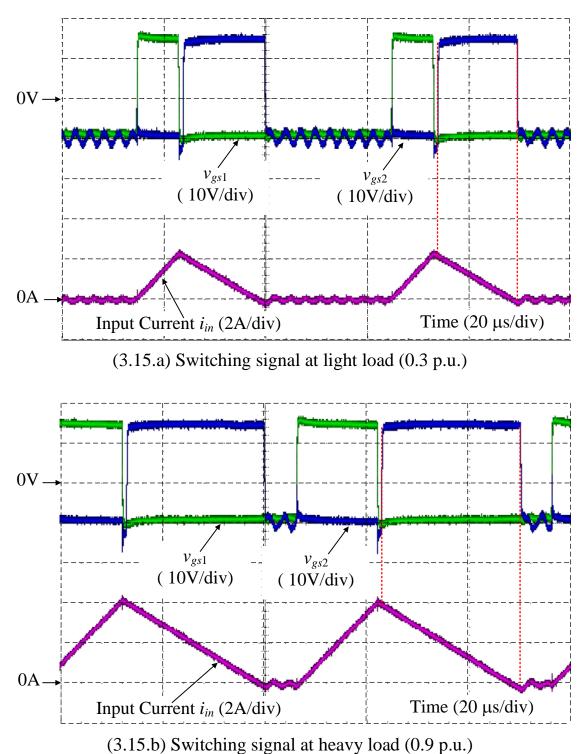

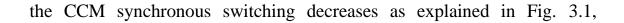

| Figure 3.15 | DCM synchronous switching 105                                  |

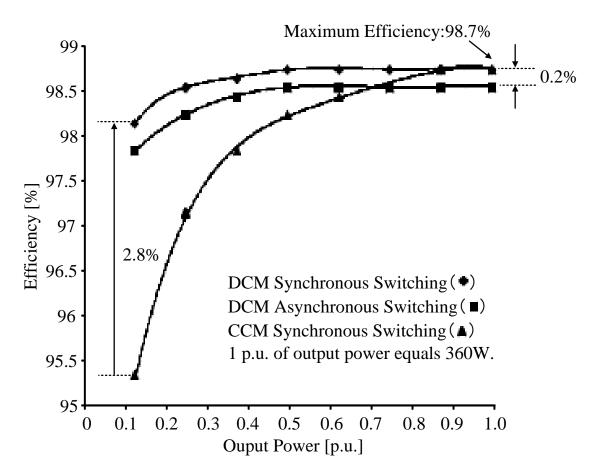

| Figure 3.16 | Efficiency comp   | arison among C | CM synchronou    | is switchir | ıg, |

|-------------|-------------------|----------------|------------------|-------------|-----|

| DCM s       | synchronous swite | ching and DCM  | I asynchronous s | witching    | 106 |

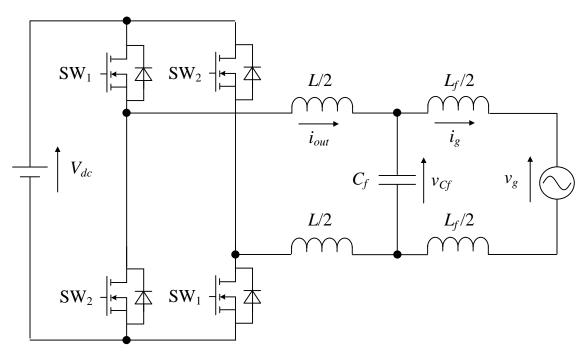

| Figure 4.1  | Single-phase grid-tied inverter 117                                 |

|-------------|---------------------------------------------------------------------|

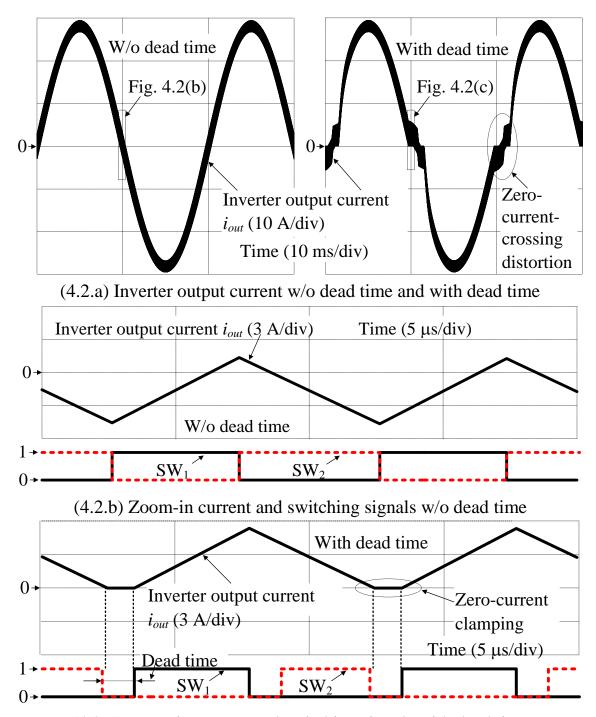

| Figure 4.2  | Zero-current clamping phenomenon and                                |

| zero-c      | urrent-crossing distortion 119                                      |

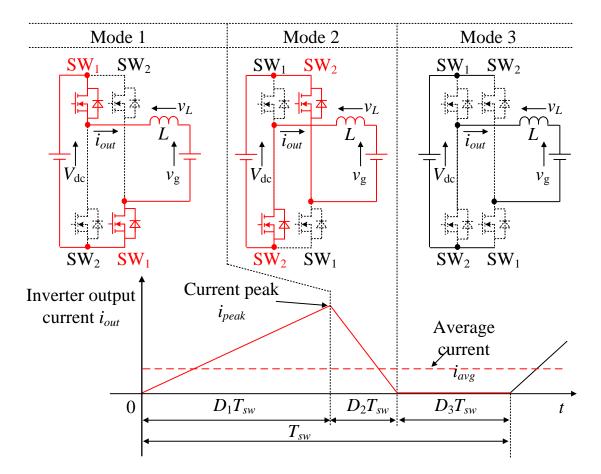

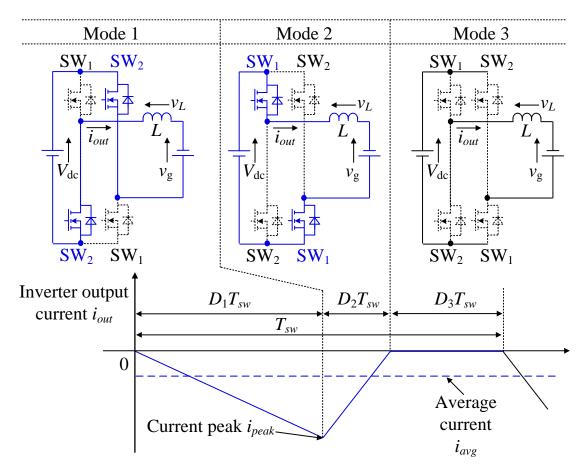

| Figure 4.3  | Current path and inverter output current waveform in DCM            |

| when t      | he grid voltage is positive125                                      |

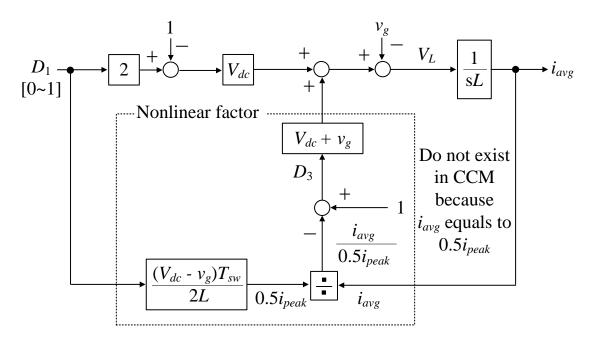

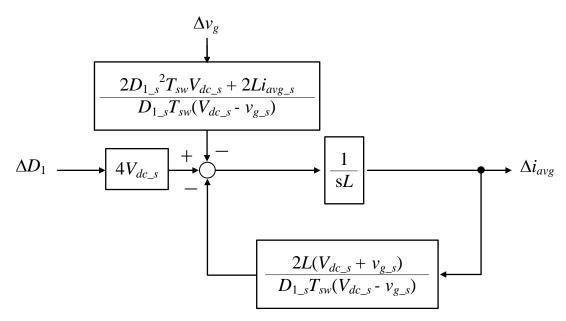

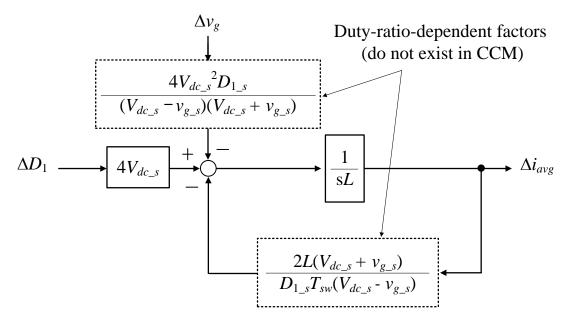

| Figure 4.4  | Circuit model of inverter operating in DCM 127                      |

| Figure 4.5  | Linearized circuit model of inverter operating in DCM ··· 129       |

| Figure 4.6  | Simplified and linearized circuit model                             |

| Figure 4.7  | Discretized circuit model of inverter operating in DCM $\cdots$ 132 |

| Figure 4.8  | Conventional and proposed DCM nonlinearity compensation             |

|             |                                                                     |

| Figure 4.9  | Current path and inverter output current waveform in DCM            |

| when t      | he grid voltage is negative                                         |

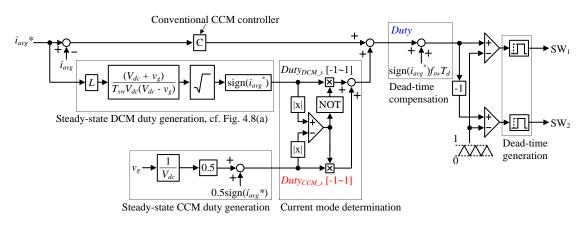

|             | Proposed DCM current control system for single-phase                |

| grid-ti     | ed inverter and variation of duty ratio in DCM137                   |

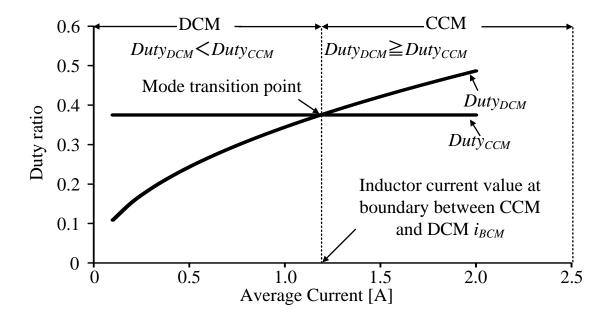

|             | Relationship among CCM duty, DCM duty and current mode              |

|             |                                                                     |

| Figure 4.12 | Conventional CCM current control system, conventional               |

| CCM&        | CM current control system, and proposed                             |

| induct      | ance-independent CCM&DCM current control system with                |

|             | orm of current mode alternation 143-144                             |

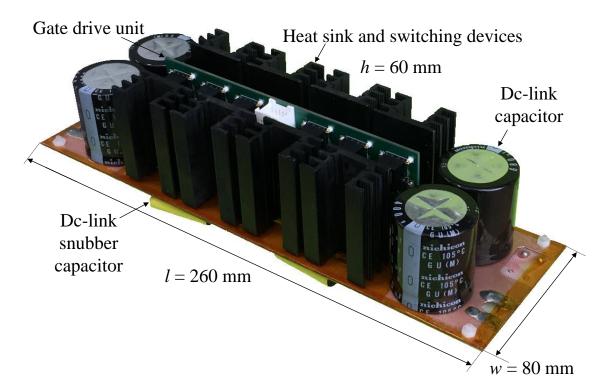

| Figure 4.13 | 4-kW 100-kHz prototype of single-phase grid-tied inverter           |

|             |                                                                     |

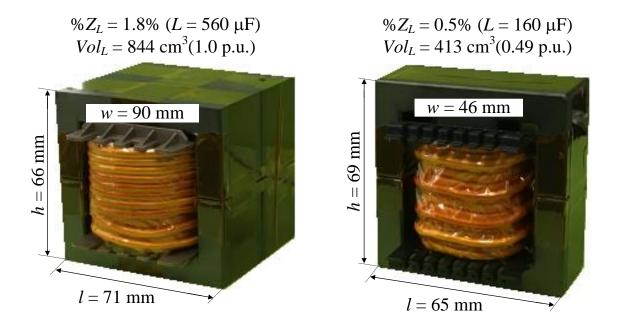

| Figure 4.14 | Prototypes of inverter-side inductors under different               |

| -           | ions of inductor impedance149                                       |

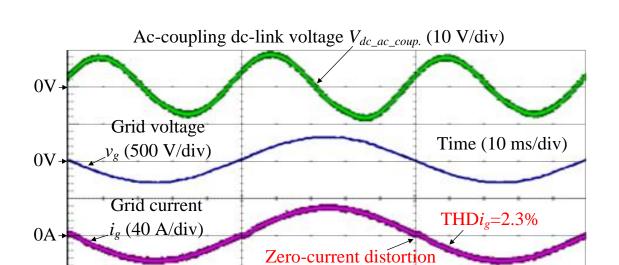

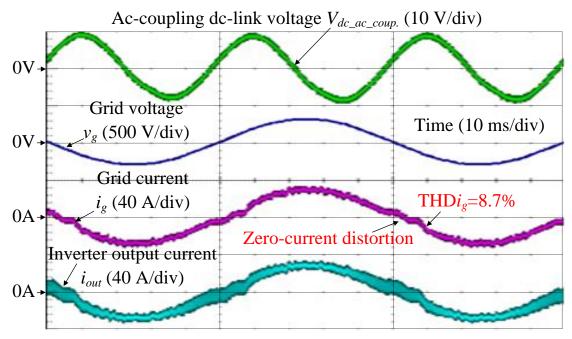

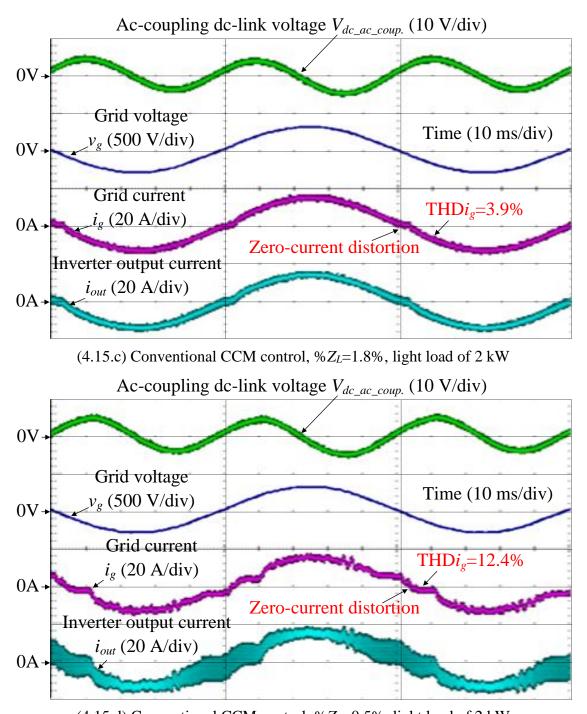

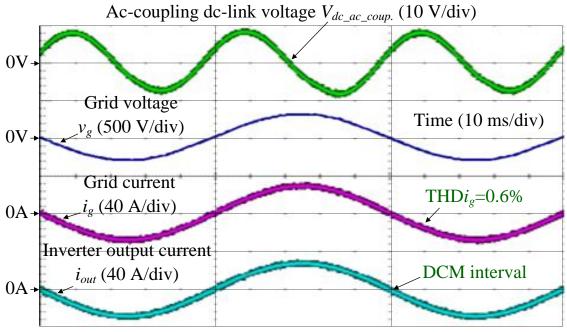

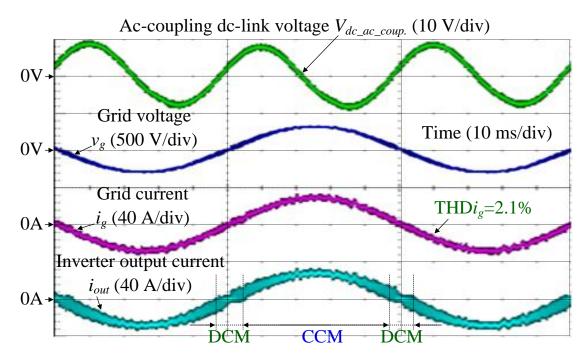

|             | Operation waveforms of conventional CCM control at rated            |

| -           | f 4 kW and at light load of 2 kW under two conditions of $\% Z_L$   |

| •••••       |                                                                     |

| Figure 4.16 | Operation waveforms of proposed CCM&DCM control at                  |

| rated l     | oad of 4 kW and at light load of 2 kW under two conditions          |

|             | L                                                                   |

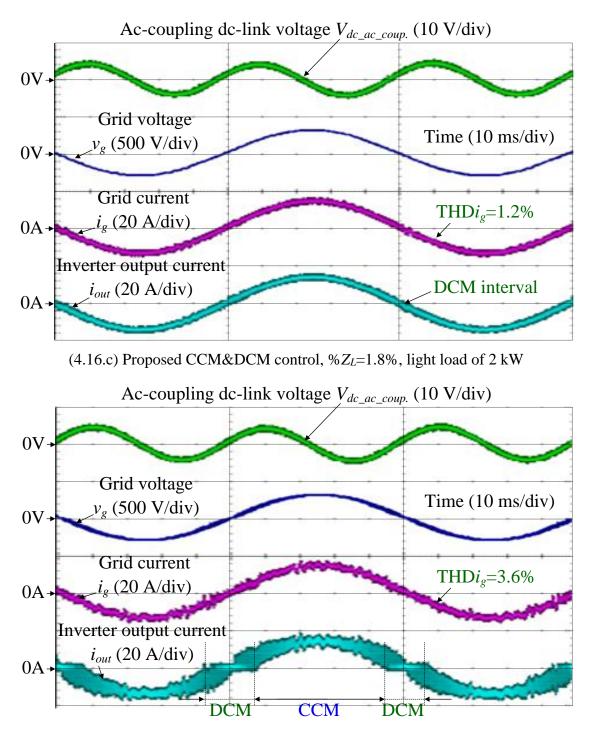

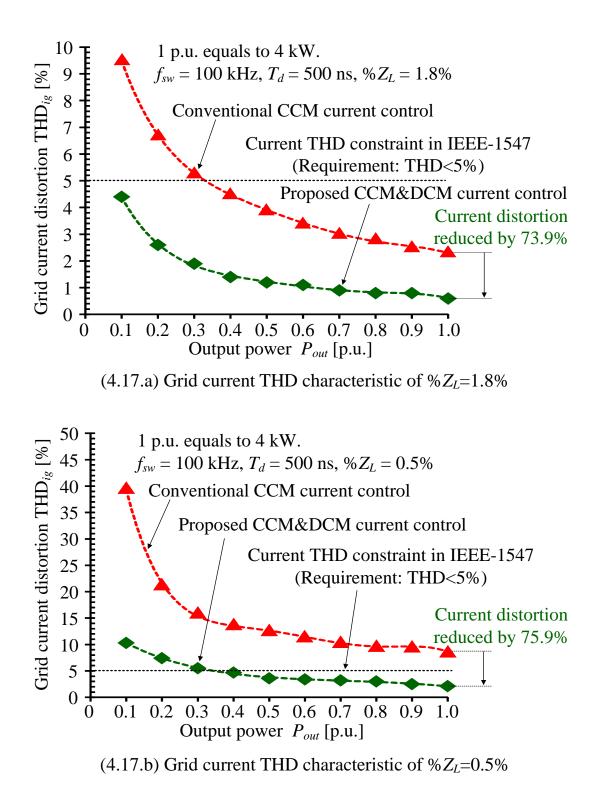

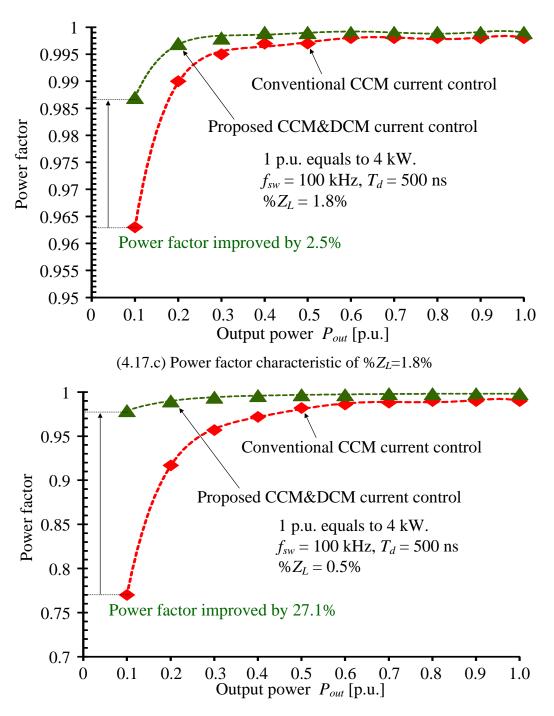

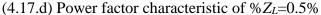

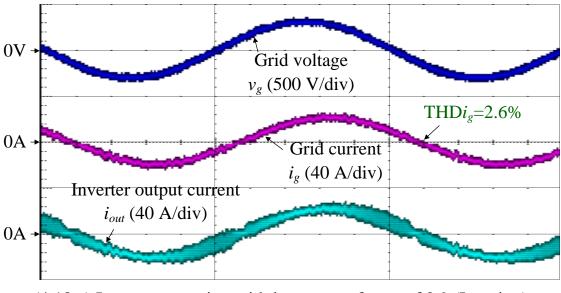

| Figure 4.17 | Grid current THD and power factor characteristics of                |

| conver      | ntional CCM current control and proposed CCM&DCM            |

|-------------|-------------------------------------------------------------|

| curren      | t control 158-159                                           |

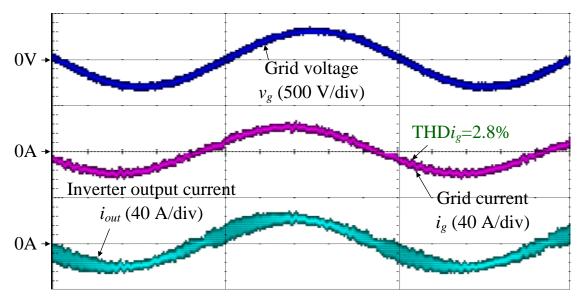

| Figure 4.18 | Proposed CCM&DCM current control operation under low        |

| power       | factor with $%Z_L$ of 0.5%                                  |

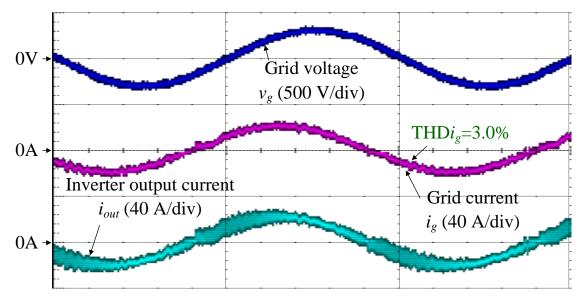

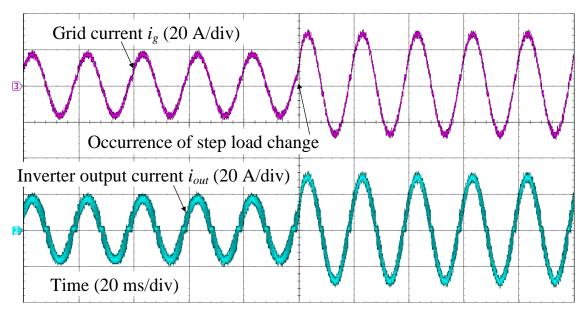

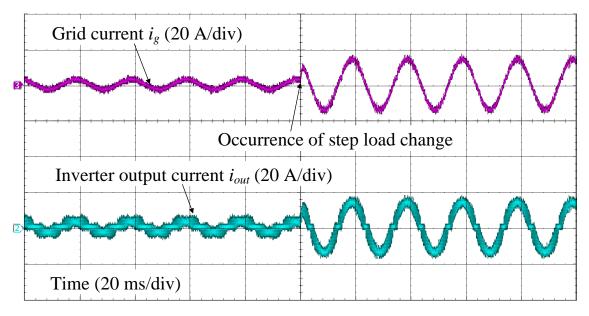

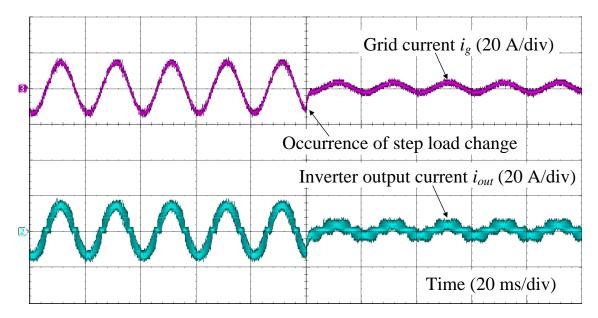

| Figure 4.19 | Proposed CCM&DCM current control operation under step       |

| load cl     | hange with $%Z_L$ of 0.5%                                   |

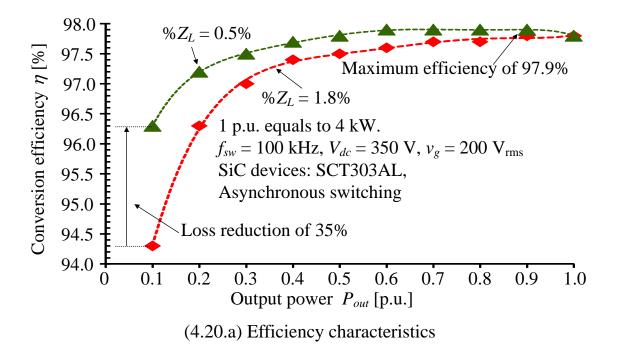

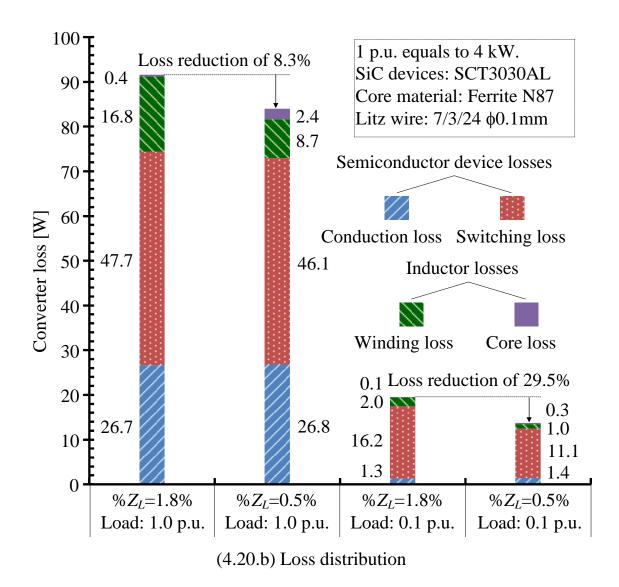

| Figure 4.20 | Efficiency and loss distribution with proposed CCM&DCM      |

| curren      | t control with $\% Z_L$ of 1.8% and 0.5% 165-166            |

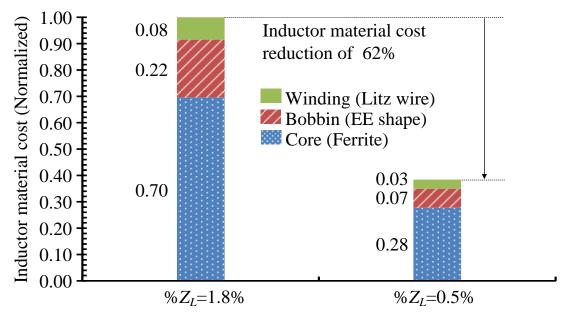

| Figure 4.21 | Cost breakdown of inverter-side inductor material under two |

| design      | s of $\% Z_L \cdots 169$                                    |

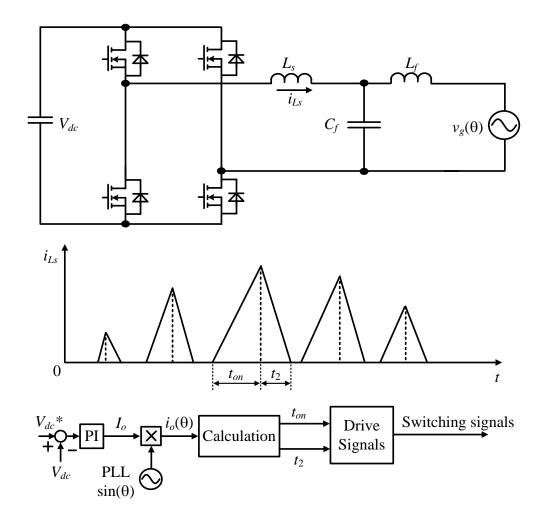

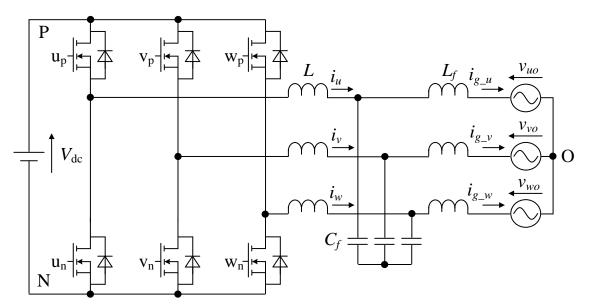

| Figure 5.1  | H-bridge grid-tied three-phase inverter                        |

|-------------|----------------------------------------------------------------|

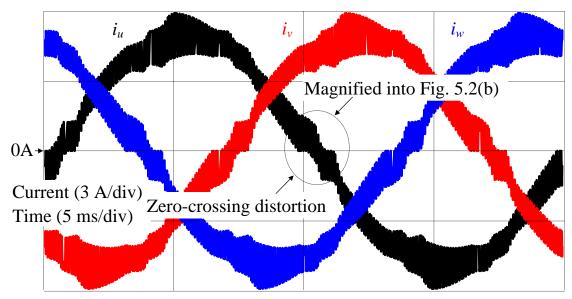

| Figure 5.2  | Zero-current distortion phenomenon 188                         |

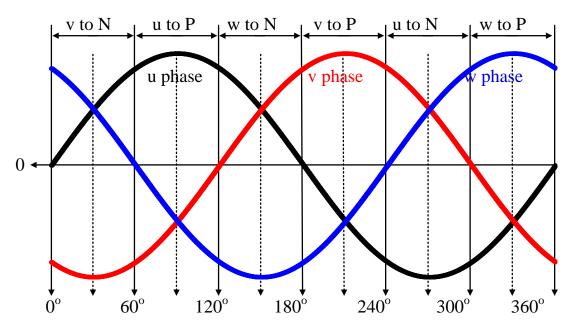

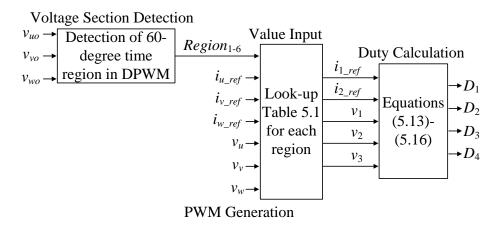

| Figure 5.3  | Six 60-degree time regions of DPWM and inverter output         |

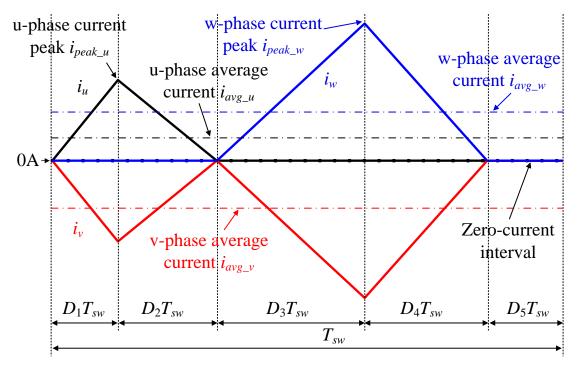

| current     | t in DCM                                                       |

| Figure 5.4  | Circuit model of inverter operating in DCM 193                 |

| Figure 5.5  | Control system of the three-phase grid-tied inverter operating |

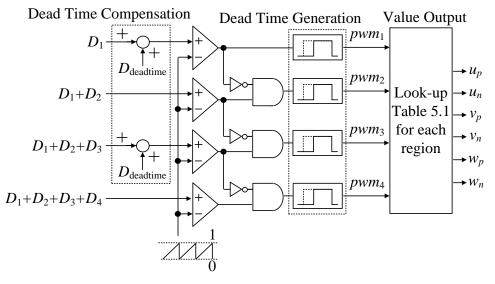

| comple      | etely in DCM 196-197                                           |

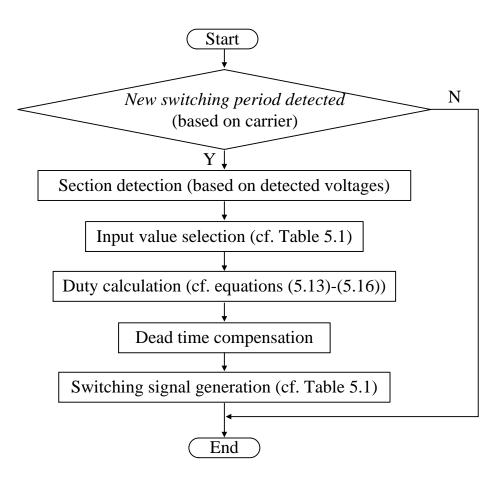

| Figure 5.6  | Relationship between filter volume and inductor impedance      |

| at swite    | ching frequency of 40 kHz····· 201                             |

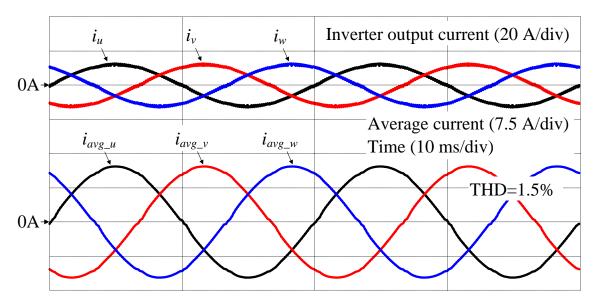

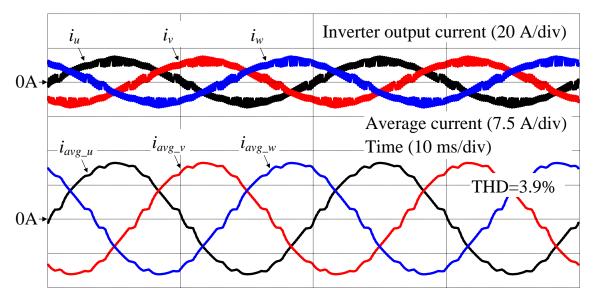

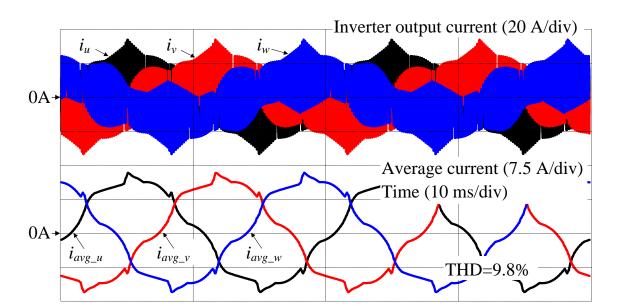

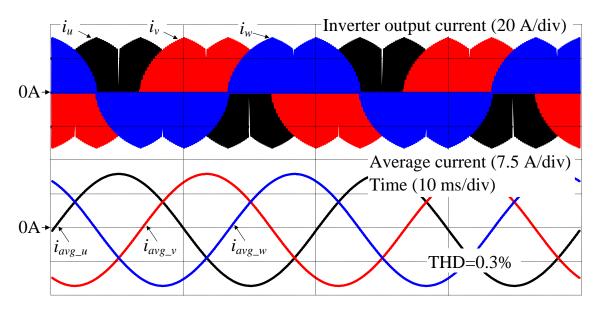

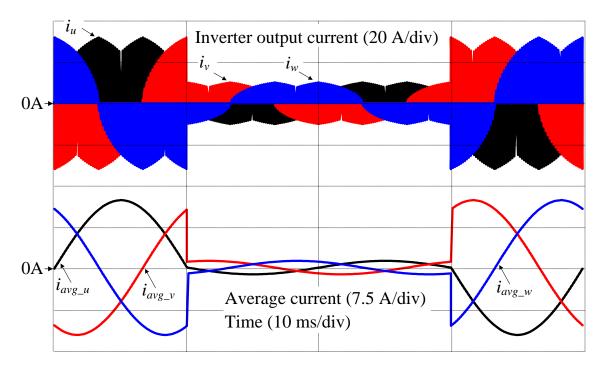

| Figure 5.7  | Inverter output currents and average currents of conventional  |

| CCM o       | current control and proposed DCM current control at rated      |

| load ···    |                                                                |

| Figure 5.8  | Load step response between load of 0.1 p.u. and load of 1.0    |

| p.u. ····   |                                                                |

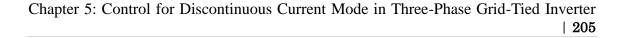

| Figure 5.9  | Current THD characteristics of conventional CCM current        |

| control     | and proposed DCM current control with three different          |

| inducto     | or designs ······ 205                                          |

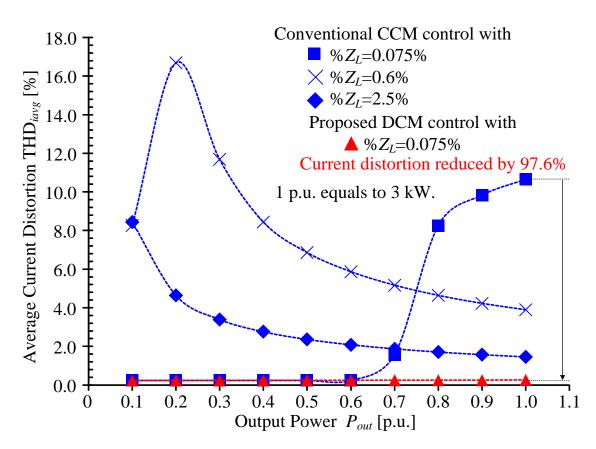

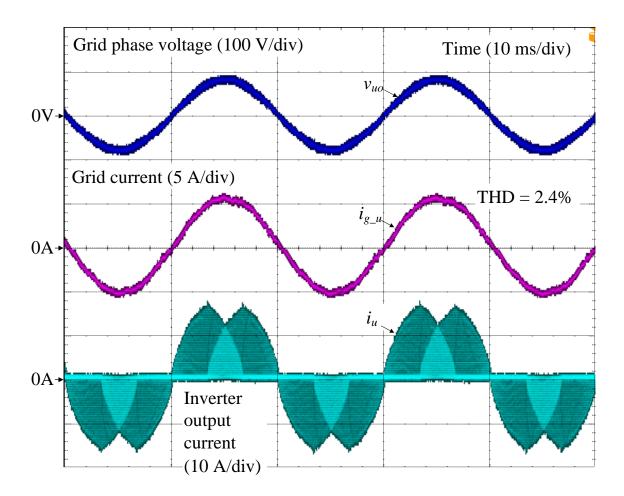

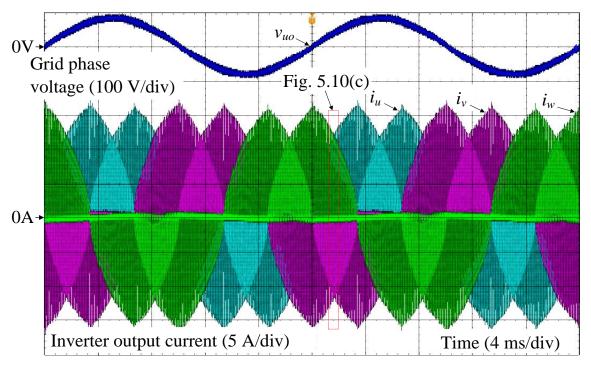

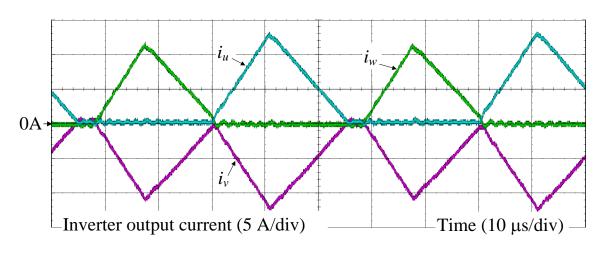

| Figure 5.10 | Prototype of miniature three-phase grid-tied inverter 207      |

| Figure 5.11 | Three-phase grid-tied inverter DCM operation waveform at       |

| rated lo    | bad                                                            |

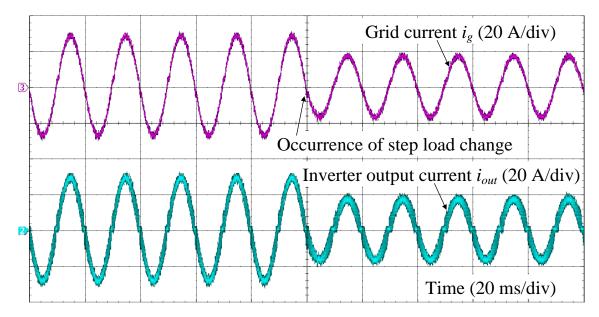

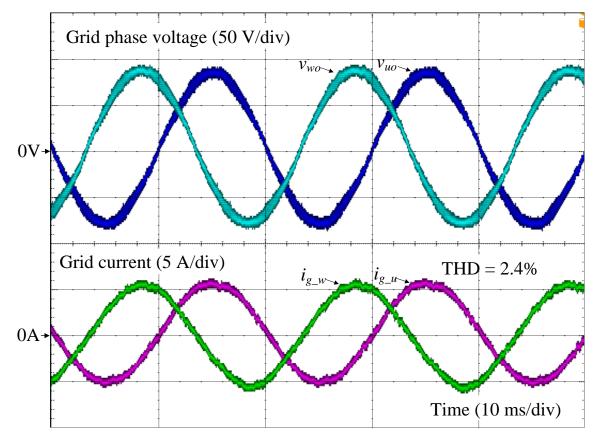

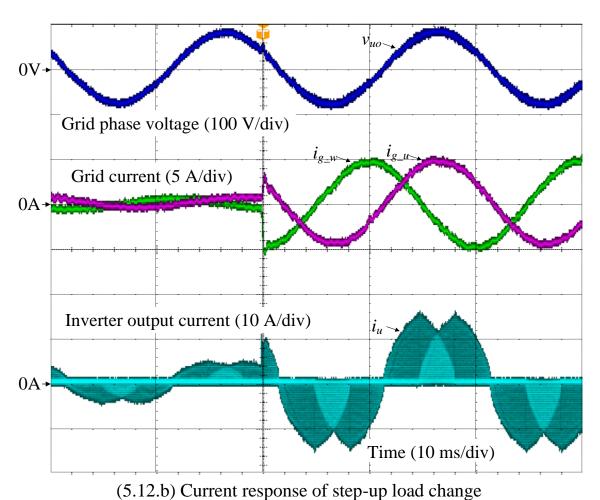

| Figure 5.12 | Grid phase voltages and grid currents of u phase and w phase   |

| at norn     | nal operation and at step-up load change210-211                |

| Figure 5.13 | Current THD characteristics of proposed DCM current            |

| control     |                                                                |

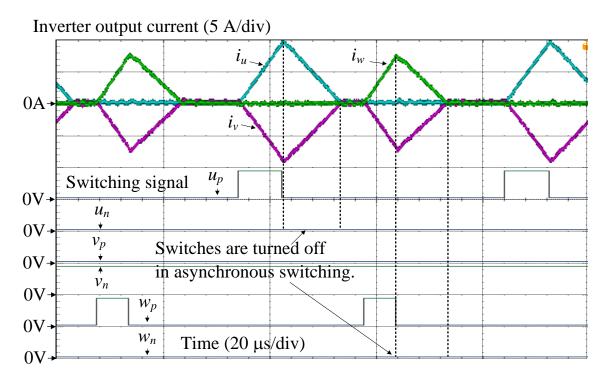

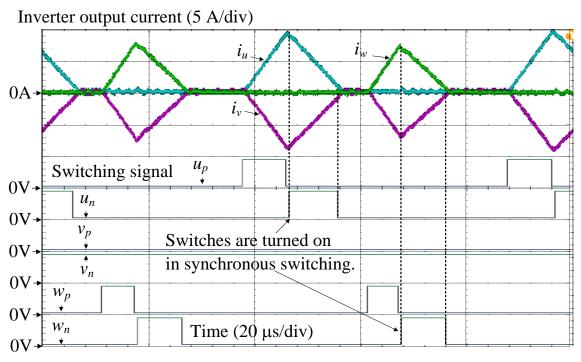

| Figure 5.14 | Asynchronous switching and synchronous switching in DCM  |

|-------------|----------------------------------------------------------|

|             |                                                          |

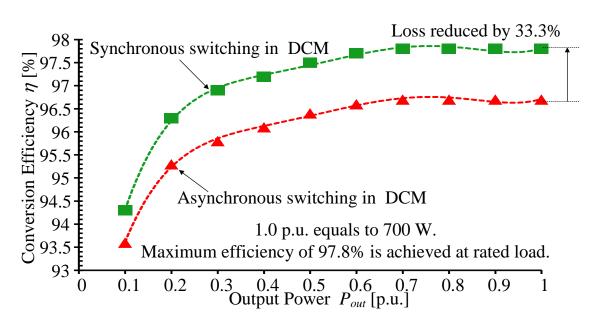

| Figure 5.15 | Efficiency comparison between asynchronous switching and |

| synchr      | onous switching in DCM ······ 215                        |

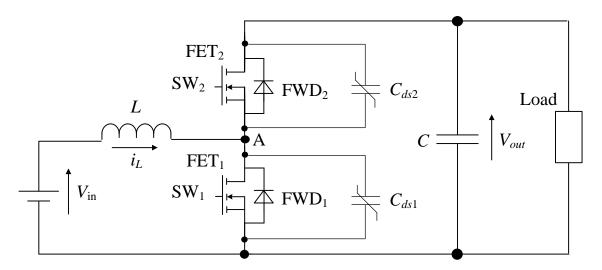

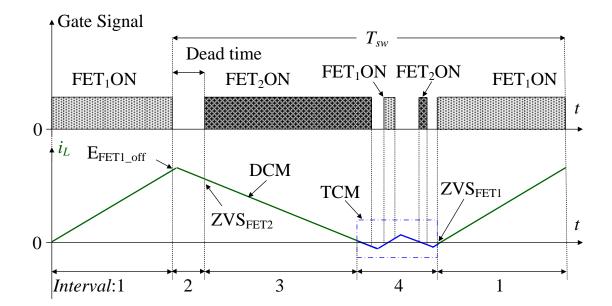

| Figure 6.1  | Typical non-isolated boost DC-DC converter                                       |

|-------------|----------------------------------------------------------------------------------|

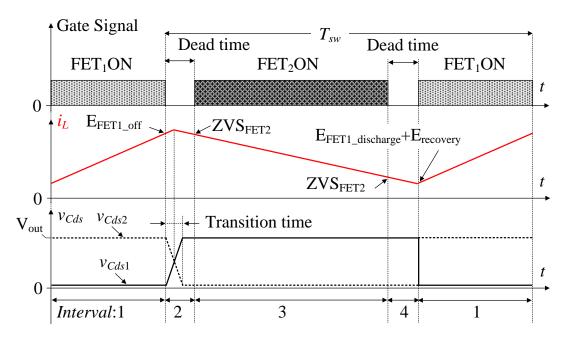

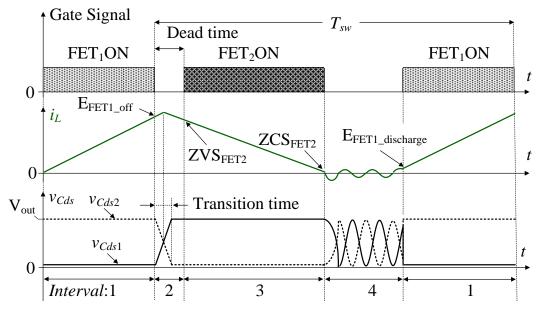

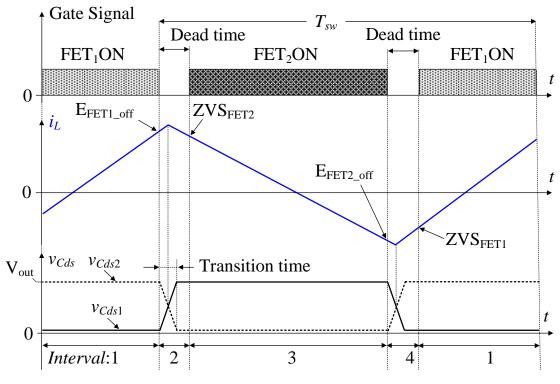

| Figure 6.2  | Switching losses in CCM, DCM and TCM 226-227                                     |

| Figure 6.3  | Hybrid discontinuous current mode between DCM and TCM                            |

|             |                                                                                  |

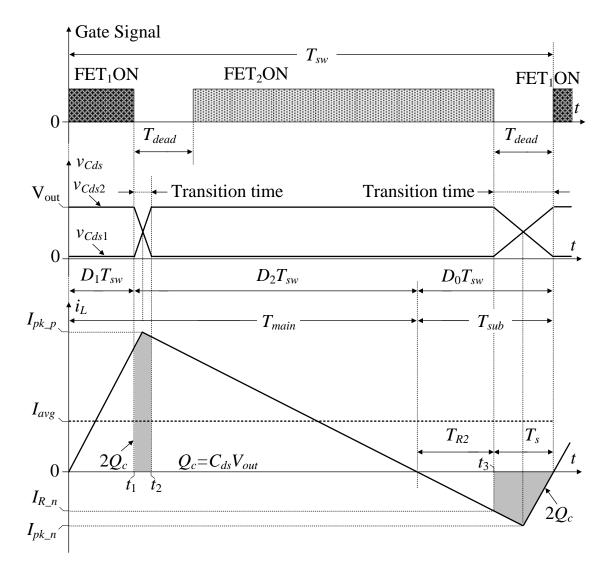

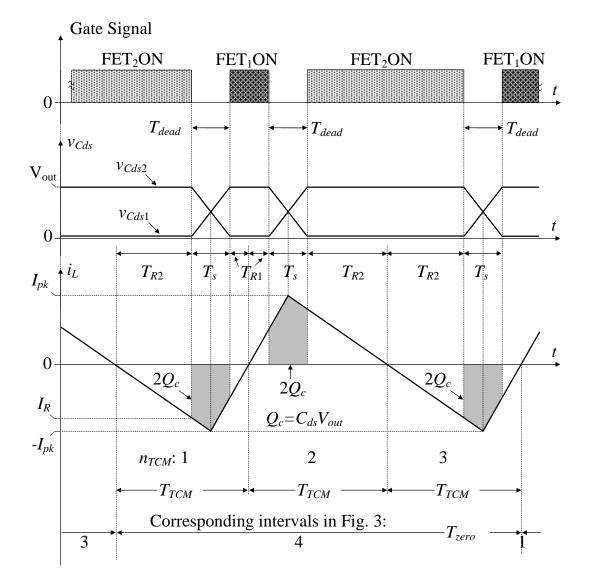

| Figure 6.4  | HDCM operation waveforms of gate signal, junction capacitor                      |

| voltag      | ge and inductor current at rated load in case of $V_{in} > V_{out}/2 \cdots 234$ |

| Figure 6.5  | Control system of boost converter operating in HDCM ···· 238                     |

| Figure 6.6  | Flowchart of switching signal generation during TCM interval                     |

| •••••       |                                                                                  |

| Figure 6.7  | HDCM operation waveforms of gate signal, junction capacitor                      |

| voltag      | ge and inductor current at light load242                                         |

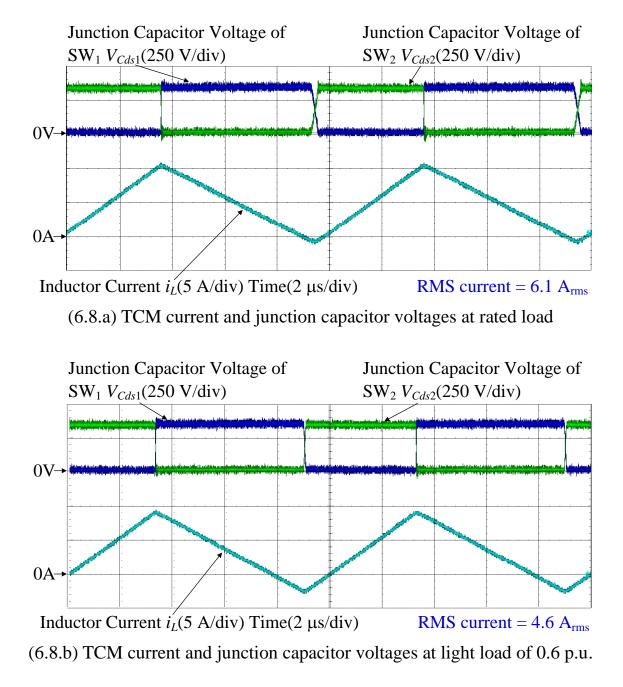

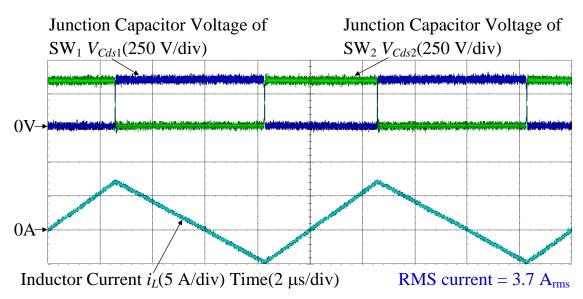

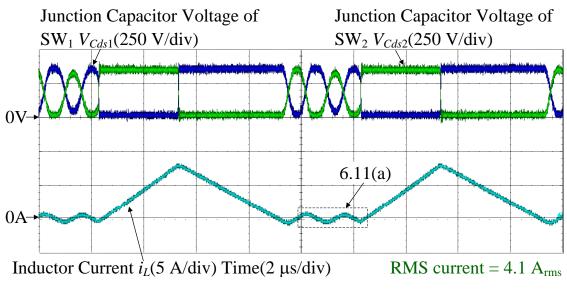

| Figure 6.8  | Waveforms of TCM current and junction capacitor voltages                         |

| under       | different conditions of load 248-249                                             |

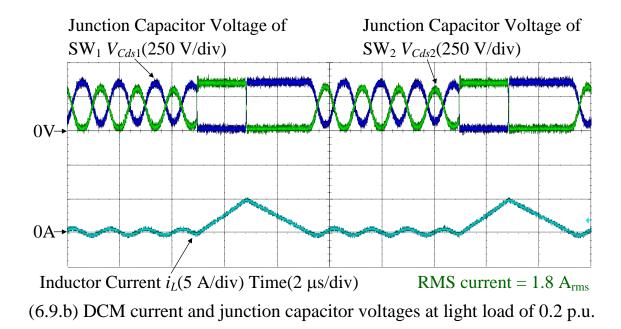

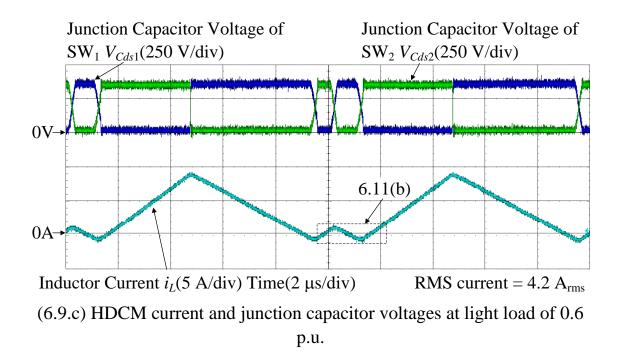

| Figure 6.9  | Waveforms of DCM and HDCM currents, and junction                                 |

| capac       | itor voltages under different conditions of load 250-251                         |

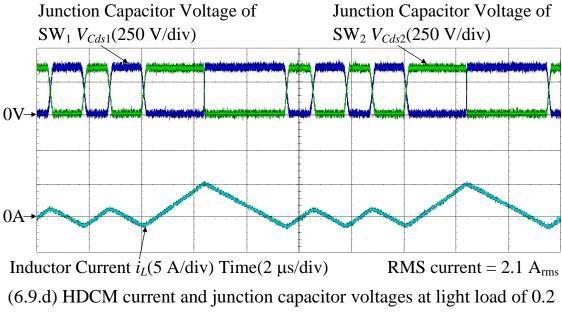

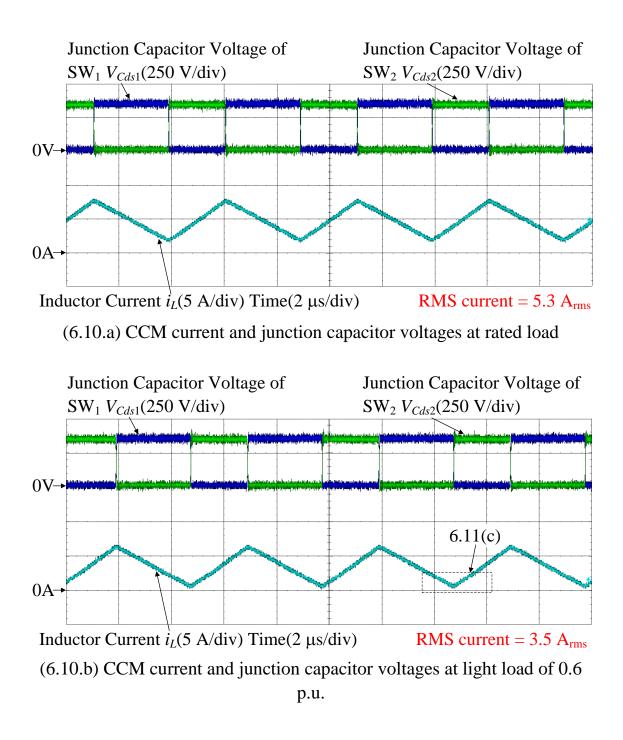

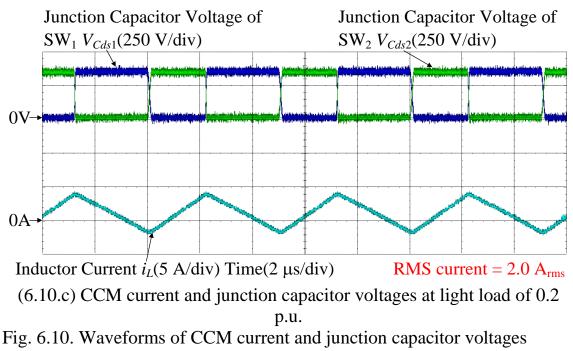

| Figure 6.10 | Waveforms of CCM current and junction capacitor voltages                         |

| under       | different conditions of load 252-253                                             |

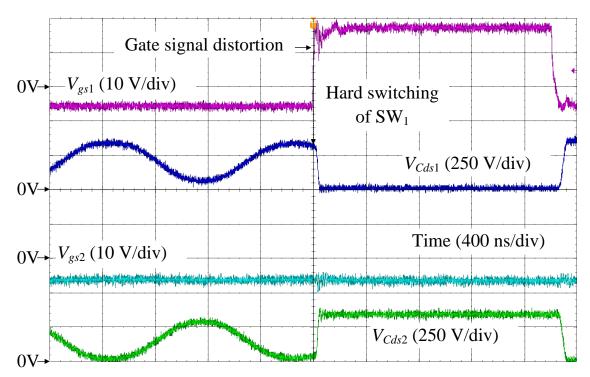

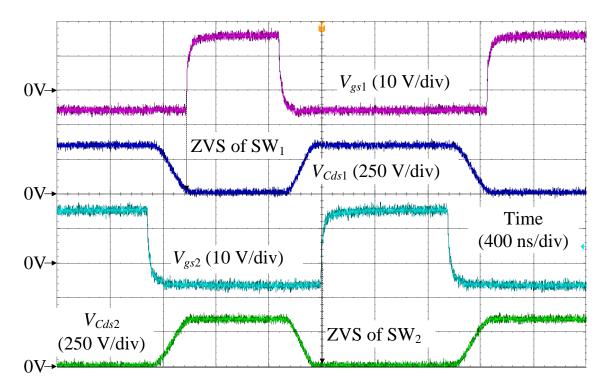

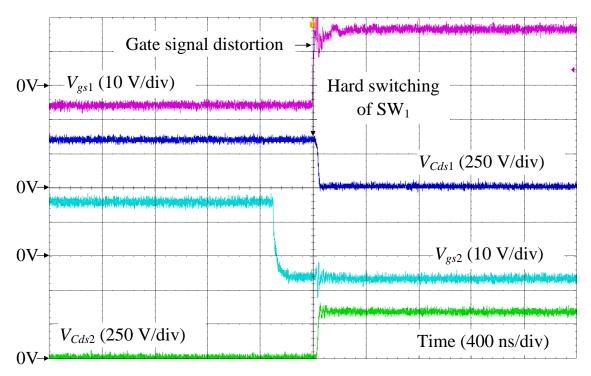

| Figure 6.11 | Waveforms of gate signal and junction capacitor voltage in                       |

| DCM         | , HDCM and CCM 255-256                                                           |

| Figure 6.12 | Comparison of RMS current and efficiency among TCM,                              |

| DCM         | , HDCM and CCM 258-259                                                           |

| Figure 6.13 | Loss distribution of four current modes under different                          |

| condit      | tions of load                                                                    |

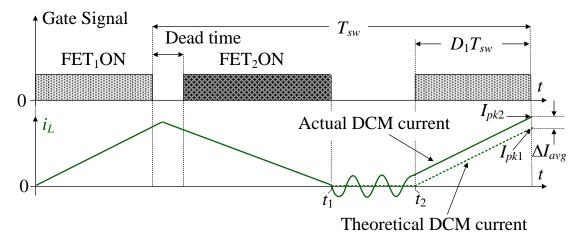

| Figure 6.14 | Theoretical and actual DCM currents                                              |

| Figure 6.15 | Average-current ripple reduction by applying HDCM265-266                         |

| Figure 6.16 | Load transient response by output voltage control with 10 Hz                     |

| cutoff      | frequency 268                                                                    |

|             |                                                                                  |

# List of Tables

#### Chapter 2

| Table 2.1 | (       | Co  | mj | pa  | ris | 501 | n ( | of | c     | 01 | n١  | ve | ent | tio | on  | al  | c  | 01 | nt | ro | 1 1 | m   | et | hc | od | <b>S</b> 1 | fo | r ( | C  | <b>C</b> ] | M   | [/ <b>I</b> | C   | 'N  | 1  |

|-----------|---------|-----|----|-----|-----|-----|-----|----|-------|----|-----|----|-----|-----|-----|-----|----|----|----|----|-----|-----|----|----|----|------------|----|-----|----|------------|-----|-------------|-----|-----|----|

| ••••      | • • • • | ••• | •• | ••• | ••• | ••• | ••• | •• | • • • | •• | ••• | •• | ••• | ••  | ••• | ••• | •• | •• | •• | •• | ••• | ••• | •• | •• | •• | ••         | •• | ••  | •• | ••         | ••• | ••          | ••• | • : | 53 |

#### Chapter 3

| Duty generation of DCM asynchronous switching and DCM                 |

|-----------------------------------------------------------------------|

| chronous switching ······ 93                                          |

| Parameters of circuit and controllers in experiments                  |

| Computation time in clock cycles for current control loop $\cdot$ 108 |

|                                                                       |

### Chapter 4

| Table 4.1 | Experimental parameters                                               |

|-----------|-----------------------------------------------------------------------|

| Table 4.2 | Minimum required dead time in consideration of maximum                |

| drain     | current, gate resistor, and maximum ambient temperature $\cdots$ 148  |

| Table 4.3 | Computation time in clock cycles of current control loop $\cdots$ 171 |

|           |                                                                       |

| Chapter 5 |                                                                       |

| Table 5.1 | Look-up table for duty calculation and PWM output 198                 |

| Table 5.2 | Simulation parameters                                                 |

| Table 5.2 | Simulation parameters   | 201 |

|-----------|-------------------------|-----|

| Table 5.3 | Experimental parameters | 206 |

| Table 6.1 | Parameters of circ | uit and controllers | s in experiments |  |

|-----------|--------------------|---------------------|------------------|--|

|-----------|--------------------|---------------------|------------------|--|

## Introduction

#### 1.1 Background

Global warming which is also referred to as climate change, is the rise in the average temperature of the Earth's climate system. The Earth's average temperature has always fluctuated and climate change is not unusual. It is the pace of global warming today that is unprecedented.

Fig. 1.1 depicts the temperature anomaly from 1880 to 2017, recorded by National Aeronautics and Space Administration (NASA) [1-1]. The Earth's temperature had already warmed by 1°C compared to pre-industrial levels. This temperature rise might appear small, but just a small rise in temperature would lead to large changes for the world's climate. According to National Geographic, the extra energy coming from just 1°C warmer could cause numerous global changes such as; e.g. the Artic is ice-free for half the year, sea level rises submerge coastal areas, hurricanes occur more frequently around the globe, severe droughts and emergence of new deserts cause shortage in global food supply, and within 85 years one third of the fresh water would be eliminated [1-2].

Fig. 1.2 depicts the atmospheric carbon dioxide concentrations in parts per million (ppm) for the past 800,000 years, recorded by National Oceanic and Atmospheric Administration (NOAA) [1-3]. It is clear that humans have caused most of the past century's warming by releasing heat-trapping gases, i.e. greenhouse gases, as we power our modern lives. Carbon dioxide is the most important of Earth's long-lived greenhouse gases. It absorbs less heat per molecule than the other greenhouse gases such as methane or nitrous oxide, but it is more abundant and it stays in the atmosphere much longer. Until the pre-industrial levels, the atmospheric carbon dioxide was never higher than 300 ppm. Over the past decade, the global growth rate of atmospheric carbon dioxide has been closer to 2.3 ppm per year, which was only  $0.6 \pm 0.1$  ppm per year in the 1960s. The annual rate of increase in atmospheric carbon dioxide over the past 60 years is about 100 times faster than previous natural increases.

Fig. 1.1. Temperature anomaly from 1880 to 2017, recorded by National Aeronautics and Space Administration (NASA). The Earth's temperature had already warmed by 1°C compared to pre-industrial levels.

Fig. 1.2. Atmospheric carbon dioxide concentrations in parts per million (ppm) for the past 800,000 years, recorded by National Oceanic and Atmospheric Administration (NOAA). It is clear that humans have caused most of the past century's warming by releasing carbon dioxide as we power our modern lives. The annual rate of increase in atmospheric carbon dioxide over the past 60 years is about 100 times faster than previous natural increases.

Fig. 1.3 depicts the U.S. greenhouse gas emissions and sinks by economic sector from 1990 to 2014, recorded by the U.S. Environmental Protection Agency (U.S. EPA) [1-4], whereas Fig. 1.4 depicts the world energy consumption by source from 1990 to 2040, recorded by the U.S. Energy Information Administration (U.S. EIA) [1-5]. Among the various sectors of the U.S. economy, electricity generation (power plants) accounts for the largest share of emissions-31 percent of total greenhouse gas emissions since 1990. Transportation is the second-largest sector, accounting for 26 percent of emissions since 1990. According to the U.S. EIA, world energy consumption will grow by 48% between 2012 and 2040. Renewables energy sources are the world's fastest-growing energy sources over the projection period, which increases by an average 2.6% per year through 2040. Even though non-fossil fuels are expected to grow faster than fossil fuels (petroleum and other liquid fuels, natural gas, and coal), fossil fuels still account for more than three-quarters of world energy consumption through 2040. In order to accelerate the employment of renewable energy sources, research on renewable energy sources should be further conducted actively and intensely.

Fig. 1.3. U.S. greenhouse gas emissions and sinks by economic sector from 1990 to 2014, recorded by the U.S. Environmental Protection Agency (U.S. EPA).

Fig. 1.4. World energy consumption by source from 1990 to 2040, recorded by the U.S. Energy Information Administration (U.S. EIA).

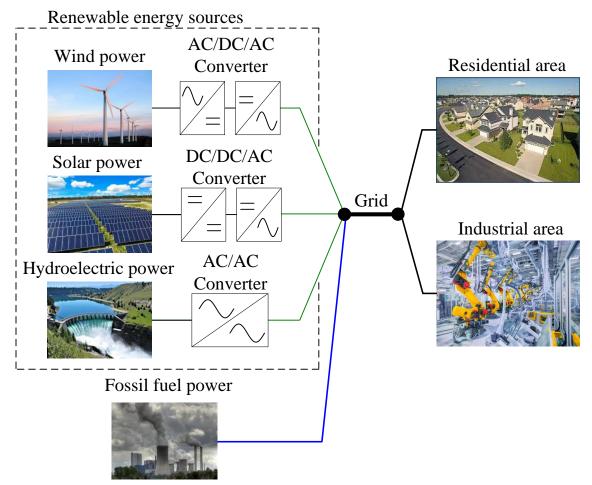

Fig. 1.5 depicts the electricity generation system employing renewable energy sources. The notable characteristic of such electricity generation system is that numerous power converters are utilized to convey the electricity power from the renewable energy sources to the electrical grid. These power converters, which can be divided into four categories as, AC/DC, DC/AC, DC/DC, and AC/AC power converters, play a vital role in renewable energy systems. Therefore, many studies focusing on these power converters are actively conducted in terms of stability, efficiency, size and cost.

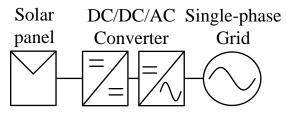

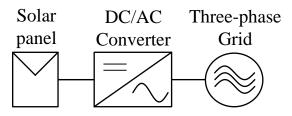

Fig. 1.6 depicts the breakdown of the solar power systems. This thesis focuses on the research of the DC/DC and DC/AC power converters in the solar power system. In particular, DC/DC converters, single-phase grid-tied inverters and three-phase grid-tied inverters are considered as the research objectives. In solar power systems, DC/DC converters achieve the maximum power point tracking in each solar cells, whereas single-phase or three-phase grid-tied inverters converts the DC power into the AC power to transmit to the electrical grid. Therefore, these converters' performance greatly contributes to the solar power system expansion.

Fig. 1.5. Electricity generation system employing renewable energy sources.

(1.6.a) Single-phase grid-tied solar power systems

(1.6.b) Three-phase grid-tied solar power systems Fig. 1.6. Breakdown of the solar power systems.

#### **1.2 Research Objectives**

Over last decades, the employment of solar power systems has accelerated due to a continuously decrease in solar panel price. In the solar power systems, typical boost DC-DC converters and grid-tied inverters are required in order to transmit solar DC power into AC single-phase grid. High efficiency and compact size with low cost are requirements for these converters and inverters in order to further assist the penetration of the solar power systems.

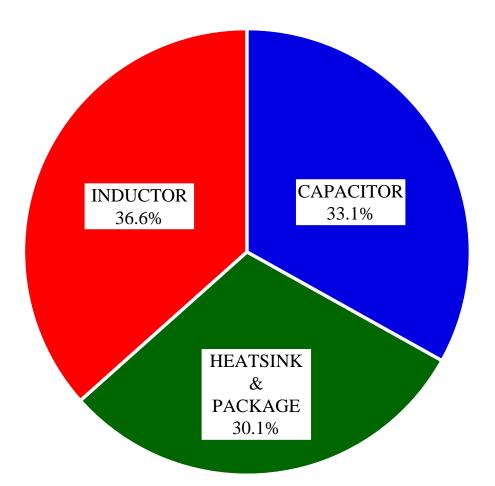

Fig. 1.7 depicts the component volume distribution in the typical boost converter with power rating of 1 kW [1-6]. The problem in the typical boost converters is the use of bulky passive components, i.e. an output capacitor and a boost inductor. One of the challenges to minimize the output capacitor is the dynamic voltage regulation during the fast load transient. In the applications for power conditioning system, the output voltage within a tight tolerance range must be maintained during the faults of the grid, i.e. a load current step occurs. The load transient requirement can be met even with small capacitance by a wide bandwidth voltage control [1-7]-[1-8]. Meanwhile, many minimization methods for the inductor have been

Fig. 1.7. Component volume distribution in the typical boost converter with power rating of 1 kW [1-6].

proposed such as high frequency switching, coupled-inductor or flyingcapacitor topologies [1-9]-[1-12]. However, higher switching frequency leads to the increase in both the switching loss and the emission noise [1-13], whereas the addition components results in the complexity of the design in the main circuit and the control method.

There are other approaches to minimize the boost inductor in terms of the operation mode. By increasing the current ripple at a given switching frequency, the typical boost converters can be operated in two main current modes; continuous current mode (CCM) and discontinuous current mode (DCM) [1-14]-[1-15]. The advantages of CCM are: simple controller design due to the linear duty-ratio-to-inductor-current transfer function, and the simple average current sampling. On the other hand, the boost converter with the DCM operation achieves the high efficiency over a wide load range because the current ripple in DCM decreases at light load. Nonetheless, the nonlinear duty-ratio-to-current transfer occurs in DCM, which worsens the current control performance when the same controller as in CCM is used. In particular, the effects of the DCM nonlinearity on the duty-ratio-to-current transfer function changes according to the current load [1-16]. This results in the overcurrent when the current is regulated by a wide bandwidth controller [1-17]. In past few years, many researches focusing on the control of DCM have been reported to solve this problem [1-18]-[1-23]. However, in those control methods, the DCM nonlinearity compensation method becomes circuit-parameter-dependent. Due to this problem, a wide bandwidth current control is still difficult to be applied into DCM. Consequently, the bandwidth of the voltage control cannot be increased in

order to minimize the output capacitor [1-24], which restricts the circuit minimization.

On the other hand, in the grid-tied inverters, *LCL* filters are generally employed between the output of the inverter and the AC single-phase grid in order to suppress current harmonics and meet grid current harmonic constraints as defined by standards such as IEEE-1547 [1-25]. Inductors in the *LCL* filters account for major volume and cost of the inverter, which can be decreased by a low-inductance *LCL* filter design [1-26]-[1-30]. However, the reduction of the inductance implies a design of a high current ripple due to a high dc-link-voltage-to-inductance ratio. This high current ripple results in a current distortion phenomenon entitled zero-current clamping, in which the current distortion increases notably as the current ripple increases [1-31]-[1-36].

When the zero-current clamping occurs, the inverter operation changes from continuous current mode (CCM) to discontinuous current mode (DCM), which is well-known for its strong nonlinear behavior. In particular, the DCM operation exhibits a nonlinear duty-ratio-to-current transfer function, which significantly changes the converter dynamic; consequently, the

current distortion increases when the same CCM controller is used to control the DCM current [1-16], [1-21], [1-37]. Similarly to the DCM operation in the boost converters, many researches focusing on compensation methods for the DCM nonlinearity have been reported to solve this problem [1-21], [1-23], [1-38]-[1-42]. However, the critical penalty of those methods is that the nonlinearity compensation for DCM is dependent on the inductance. In the solar power systems, the inductors with high tolerance are generally employed in the inverter; furthermore, the grid-tied inverter is required to deal with severe changes of the ambience, i.e. the inductance varies frequently. When actual inductances are different from nominal values, the stability of such inductance-dependent control methods can no longer be guaranteed. In general, the inductance-dependent control bandwidth is designed to be low to ensure the stability, restricting the application of the DCM operation. On the other hand, the inductance-independent control for the DCM operation can compensate the DCM nonlinearities while still achieving a wide control bandwidth because the inductance toleration no longer has a significant effect on the control stability. Consequently, the

inductance-independent DCM control is essential for expanding the

employment of the DCM operation.

The objective of this research is to minimize the inductors in the solar power systems. The inductance reduction is accomplished by the lowfrequency high-current-ripple design, leading to the operation of DCM. Consequently, the solar power systems benefit in term of size and efficiency because the high-switching-frequency design is unnecessary to minimize the inductance.

First of all, the inductance-independent control of DCM is studied. As previously discussed, the DCM operation enables the inductor minimization even at the low switching frequency because this operation mode features a low-frequency high-current-ripple design. Furthermore, the DCM operation also provides an efficiency improvement at light load due to the loaddependent decrease in current ripple. However, the application of the DCM operation still remains inactive. One of the reason is the occurrence of the nonlinearity in the DCM operation; this makes the converter control become inductance-dependent. Consequently, the control bandwidth of the DCM operation is generally low to ensure the converter stability. This research focuses on the inductance-independent nonlinearity compensation for the DCM operation. If the nonlinearity in the DCM operation is completely compensated independently from the inductance, the same controller designed in the CCM operation can be applied and the same control bandwidth as in CCM can be achieved.

Then, the mode transition between the CCM and DCM operation is studied. Similarly, the inductance-independently current mode detection between CCM and DCM is necessary when the inverter is designed to operate in both CCM and DCM. When both the current mode detection and the DCM nonlinearity compensation becomes independently from the inductance, the employment of the proposed control method is no longer restricted. Consequently, the inductor can be actively minimized due to the application of the DCM operation.

Finally, the hybrid current mode between DCM and triangular current mode (TCM) is studied. The hard switching on turn-on still occurs in CCM and DCM; this restricted the design of the high switching frequency to further minimize the inductors. The hybrid current mode between DCM and TCM achieves both zero-voltage-switching (ZVS) and current reduction at light load. Therefore, the high efficiency is achieved over wide load range.

#### **1.3 Thesis Outline**

Fig. 1.8 shows the outline of this thesis divided into 7 chapters. Chapter 1 introduces the importance of the renewable energy sources being the key to fight against global warming issue. Next, the power converter role in such renewable energy sources is discussed. In particular, the power conversion in the solar power systems is focused in this research. Then, the objectives to minimize the inductors in the solar power systems are demonstrated.

Chapter 2 reviews the state of arts of current control for CCM and DCM, and propose the novel method. First, the DCM control challenges in DC-DC converters, and single-phase and three-phase DC-AC converters are discussed and then following by the conventional inductance-dependent control for CCM and DCM. Then, the inductance-independent control for CCM and DCM are proposed with the hybrid DCM. The original idea in this thesis is that the DCM nonlinearity compensation is constructed by utilizing a duty ratio at a previous calculation period instead of using the inductance. Furthermore, the current mode is also determined without using the inductance by the comparison of the output duty ratios. After that, the beneficial position of the proposed method compared with the conventional

Fig. 1.8. Outline of the thesis.

method is discussed. Finally, the conclusion of the chapter is provided.

Chapter 3 discusses the proposed DCM control for boost converter as an

example for DC-DC converters. First, the design of the conventional PI controller is explained because the proposed DCM control is based on the

CCM control with a PI controller, next the inductance-independent DCM nonlinearity compensation method is proposed as the main part of this chapter. Then, the validity of the proposed DCM nonlinearity compensation method is verified. In addition, in order to achieve higher efficiency in the boost converter, the simple DCM synchronous switching method is realized based on the proposed DCM current control. After that, the comparisons of the efficiencies and the current-control computation time are demonstrated in order to confirm the effectiveness of the proposed DCM current control. Finally, the conclusion for the chapter is provided.

Chapter 4 discusses the proposed CCM/DCM control for single-phase grid-tied inverter. First, the zero-current clamping phenomenon is explained together with the problems of the conventional DCM nonlinearity compensation methods, then the CCM/DCM current control based on the inductance-independent DCM nonlinearity compensation is proposed as the main part of this chapter. Next, the mechanism of the current mode detection without using the inductance is explained. After that, the effectiveness of the proposed CCM/DCM current control is confirmed. Finally, the conclusion for the chapter is provided.

Chapter 5 discusses the proposed DCM control for three-phase grid-tied inverter. First, the circuit model for DCM is derived, and following by the proposed DCM control system. Next, the effectiveness of the proposed DCM control is confirmed by simulation. After that, the operation of the proposed DCM control is experimentally verified together with the efficiency comparison. Finally, the conclusion for the chapter is provided.

Chapter 6 discusses the hybrid DCM. First, the drawbacks of the conventional current mode are provided, and following by the hybrid current mode between DCM and TCM. Next, the generation and control of the hybrid DCM is demonstrated. After that, the operation of the hybrid DCM is experimentally verified together with the comparisons of root-mean-square current and efficiency. Finally, the conclusion for the chapter is provided.

Chapter 7 provides the conclusion for the thesis. In this chapter, the advantages and drawbacks of the proposed converter are classified clearly. The present works are summarized and future works which are expected to be carried out will be discussed.

# **Bibliography**

- [1-1] NASA's Goddard Institute for Space Studies (GISS), "GLOBAL LAND-OCEAN TEMPERATURE INDEX," 2017 [Partially Online], available: https://climate.nasa.gov/vital-signs/global- temperature/

- [1-2] National Geographic, "CAUSES AND EFFECTS OF CLIMATE CHANGE," 2017 [Partially Online], available: https://www. nationalgeographic.com/environment/global-warming/globalwarming-effects/

- [1-3] Rebecca Lindsey, "Climate Change: Atmospheric Carbon Dioxide," August 2018 [Partially Online], available: https://www. climate.gov/news-features/understanding-climate/climate-changeatmospheric-carbon-dioxide

- [1-4] U.S. Environmental Protection Agency, "Climate Change Indicators: U.S. Greenhouse Gas Emissions," August 2016 [Partially Online], available: https://www.epa.gov/climate- indicators/climate-changeindicators-us-greenhouse-gas-emissions

- [1-5] U.S. Energy Information Administration, "EIA projects 48% increase in world energy consumption by 2040," May 2016 [Partially Online], available: https://www.eia.gov/todayinenergy/ detail.php?id=26212

- [1-6] J. Itoh, T. Sakuraba, H. Watanabe and N. Takaoka, "DC to singlephase AC grid-tied inverter using buck type active power decoupling without additional magnetic component," 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, 2017, pp. 1765-1772.

- [1-7] K. Yao, Y. Ren, and F. C. Lee, "Critical Bandwidth for the Load Transient Response of Voltage Regulator Modules," *IEEE Trans. Power Electron.*, vol. 19, no. 6, pp. 1454-1461, Nov. 2004.

- [1-8] B. A. Ferrari, N. R. N. Ama, K. C. M. Carvalho, F. O. Martinz, and L. M. Junior, "Robust Control Design for Voltage Tracking Loop of Dynamic Voltage Restorers," *IEEJ J. Ind. Appl.*, vol. 4, no. 5, pp. 634-642, Sep. 2015.

- [1-9] R. C. N. Pilawa-Podgurski, A. D. Sagneri, J. M. Rivas, D. I. Anderson, and D. J. Perreault, "Very-High-Frequency Resonant Boost Converters," *IEEE Trans. Power Electron.*, vol. 24, no. 6, pp. 1654-1665, Jun. 2009.

- [1-10] H. Kosai, S. McNeal, B. Jordan, J. Scofield, B. Ray, and Z. Turgut, "Coupled Inductor Characterization for a High Performance Interleaved Boost Converter," *IEEE Trans. Magnetics*, vol. 45, no. 10, pp. 4812-4815, Oct. 2009.

- [1-11] A. B. Ponniran, K. Matsuura, K. Orikawa, and J. Itoh, "Size reduction of DC-DC converter using flying capacitor topology with small capacitance," *IEEJ J. Ind. Appl.*, Vol. 3, No. 6, pp. 20-30, Nov. 2014.

- [1-12] J. Imaoka, M. Yamamoto, and T. Kawashima, "High-Power-Density Three-phase Interleaved Boost Converter with a Novel Coupled Inductor," *IEEJ J. Ind. Appl.*, vol. 4, no. 1, pp. 20-30, Jan. 2015.

- [1-13] T. Masuzawa, E. Hoene, S. Hoffmann, and K. Lang, "Modeling Method of Stray Magnetic Couplings in an EMC Filter for Power Electronic Devices", *IEEJ J. Ind. Appl.*, vol. 4, no. 6, pp. 738-744, Nov. 2015.

- [1-14] J. Zhang, J. Sh. Lai, R. Y. Kim, and W. Yu, "High-Power Density Design of a Soft-Switching High-Power Bidirectional dc-dc

Converter", *IEEE Trans. Power Electron.*, vol. 22, no. 4, pp. 1145-1153, Jul. 2007.

- [1-15] L. Ni, D. J. Patterson, and J. L. Hudgins, "High Power Current Sensorless Bidirectional 16-Phase Interleaved DC-DC Converter for Hybrid Vehicle Application," *IEEE Trans. Power Electron.*, vol. 27, no. 3, pp. 1141-1151, Mar. 2012.

- [1-16] Jian Sun, Daniel M. Mitchell, Matthew F. Greuel, Philip T. Krein, and Richard M. Bass: "Averaged Modeling of PWM Converters Operating in Discontinuous Conduction Mode," *IEEE Trans. Power Electron.*, vol.16, no. 4, pp.482-492, Jul. 2001.

- [1-17] A. Saysanasongkham, M. Arai, S. Fukumoto, S. Takeuchi, and K. Wada, "A Highly Reliable Digital Current Control using an Adaptive Sampling Method," *IEEJ J. Ind. Appl.*, vol. 3, no. 4, pp. 296-303, Jul. 2014.

- [1-18] T. S Hwang, and S. Y. Park, "Seamless Boost Converter Control Under the Critical Boundary Condition for a Fuel Cell Power Conditioning System," *IEEE Trans. Power Electron.*, vol. 27, no. 8, pp. 3616-3626, Aug. 2012.

- [1-19] J. W. Shin, and B. H. Cho, "Digitally Implemented Average Current-Mode Control in Discontinuous Conduction Mode PFC Rectifier," *IEEE Trans. Power Electron.*, vol. 27, no. 7, pp. 3363-3373, Jul. 2012.

- [1-20] K. D. Gusseme, D. M. V. de Sype, A. P. V. den Bossche, J. A. Melkebeek, "Sample correction for digitally controlled boost PFC converters operating in both CCM and DCM," in *Proc. 18th Annu. IEEE Appl. Power Electron. Conf. Expo.*, Feb. 2003, pp. 389–395.

- [1-21] K. D. Gusseme, D. M. V. de Sype, A. P. V. den Bossche, and J. A. Melkebeek, "Digitally Controlled Boost Power-Factor-Correction Converters Operating in Both Continuous and Discontinuous Conduction Mode," *IEEE Trans. Power Electron.*, vol. 52, no. 1, pp.

88-97, Feb. 2005.

- [1-22] Sh. F. Lim, and A. M. Khambadkone, "A Simple Digital DCM Control Scheme for Boost PFC Operating in Both CCM and DCM," *IEEE Trans. Power Electron.*, vol. 47, no. 4, pp. 1802-1812, Aug. 2011.

- [1-23] C. W. Clark, F. Musavi, and W. Eberle, "Digital DCM Detection and Mixed Conduction Mode Control for Boost PFC Converters," *IEEE Trans. Power Electron.*, vol. 29, no. 1, pp. 347-355, Jan. 2014.

- [1-24] S. W. Kang, H. J. Kim, and B. H. Cho, "A Dual-Loop Voltage Control for Optocoupler Feedback in Capacitive Output Filter Converter," in *Proc. IEEE Energy Convers. Congr. Expo.*, Oct. 2015, pp. 20-24.

- [1-25] IEEE Application Guide for IEEE Std 1547, IEEE Standard for Interconnecting Distributed Resources With Electric Power Systems, IEEE Standard 1547.2-2008, 2009.

- [1-26] M. Liserre, F. Blaabjerg and S. Hansen, "Design and control of an LCL-filter-based three-phase active rectifier," in *IEEE Transactions* on *Industry Applications*, vol. 41, no. 5, pp. 1281-1291, Sept.-Oct. 2005.

- [1-27] G. Zeng, T. W. Rasmussen, and R. Teodorescu, "A novel optimized LCL-filter designing method for grid connected converter," in Proc. 2nd IEEE Int. Symp. Power Electron. Distrib. Generat. Syst., vol. 2, Jun. 2010, pp. 802–805.

- [1-28] J. Verveckken, J. F. Silva, and J. Driesen, "Optimal analytic LCL filter design for grid-connected voltage-source converter," in *Proc. EuroCon*, Jul. 2013, pp. 823–830.

- [1-29] L. Shen, G. Asher, P. Wheeler, and S. Bozhko, "Optimal LCL filter design for 3-phase space vector PWM rectifiers on variable frequency aircraft power system," in *Proc. 15th Eur. Conf. Power*

*Electron. Appl. (EPE)*, Sep. 2013, pp. 1–8.

- [1-30] R. A. Barrera-Cardenas, J. Zhang, T. Isobe and H. Tadano, "A comparative study of output filter efficiency and power density in Single-Phase Grid-Tied Inverter using continuous or discontinuous current mode operations," in *Proc. 19th Eur. Conf. Power Electron. Appl. (EPE)*, Sep. 2017, pp. 1-10.

- [1-31] J.-W. Choi and S.-K. Sul, "A new compensation strategy reducing voltage/current distortion in PWM VSI systems operating with low output voltages," in *IEEE Trans. Ind. Appl.*, vol. 31, no. 5, pp. 1001– 1008, Sep./Oct. 1995.

- [1-32] S. Bolognani, L. Peretti, and M. Zigliotto, "Repetitive-control-based selfcommissioning procedure for inverter nonidealities compensation," in *IEEE Trans. Ind. Appl.*, vol. 44, no. 5, pp. 1587– 1596, Sep./Oct. 2008.

- [1-33] J. Schellekens, R. Bierbooms, and J. Duarte, "Dead-time compensation for PWM amplifiers using simple feed-forward techniques," in *Proc. XIX Int. Conf. Electr. Mach.*, Sep. 2010, pp. 1– 6.

- [1-34] Y. wang, Q. Gao, and X. Cai, "Mixed PWM modulation for deadtime elimination and compensation in a grid-tied inverter," in *IEEE Trans. Ind. Electron.*, vol. 58, no. 11, pp. 4797–4803, Oct. 2011.

- [1-35] M. A. Herran, J. R. Fischer, S. A. Gonzalez, M. G. Judewicz and D. O. Carrica, "Adaptive Dead-Time Compensation for Grid-Connected PWM Inverters of Single-Stage PV Systems," in *IEEE Transactions* on Power Electronics, vol. 28, no. 6, pp. 2816-2825, June 2013.

- [1-36] H. Haga, K. Sayama, K. Ohishi, and T. Shimizu, "Fine Voltage Control Based on Frequency Separation Two-Degrees-of-Freedom Control for Single-Phase Inverter," in IEEJ Industry Applications, vol. 5, no. 6, pp. 413-421, 2016.

- [1-37] H. N. Le, K. Orikawa and J. I. Itoh, "Circuit-Parameter-Independent Nonlinearity Compensation for Boost Converter Operated in Discontinuous Current Mode," in *IEEE Transactions on Industrial Electronics*, vol. 64, no. 2, pp. 1157-1166, Feb. 2017.

- [1-38] M. A. Herran, J. R. Fischer, S. A. Gonzalez, M. G. Judewicz and D. O. Carrica, "Adaptive Dead-Time Compensation for Grid-Connected PWM Inverters of Single-Stage PV Systems," in *IEEE Transactions* on Power Electronics, vol. 28, no. 6, pp. 2816-2825, June 2013.

- [1-39] T. Mannen and H. Fujita, "Dead-Time Compensation Method Based on Current Ripple Estimation," in *IEEE Transactions on Power Electronics*, vol. 30, no. 7, pp. 4016-4024, July 2015.

- [1-40] K. D. Gussemé, David. M. V. D. Sype, A. P. M. V. D. Bossche, J. A. Melkebeek, "Input-Current Distortion of CCM Boost PFC Converters Operated in DCM," in *IEEE Trans. Power Electron.*, vol. 54, no. 2, pp. 858-865, Apr. 2007.

- [1-41] D. Yamanodera, T. Isobe and H. Tadano, "Application of GaN device to MHz operating grid-tied inverter using discontinuous current mode for compact and efficient power conversion," in *Proc. 12th Int. Conf. Power Electron. Drive Systems (PEDS)*, Dec. 2017, pp. 1003-1009.

- [1-42] Y. Kwon, J. Park, and K. Lee, "Improving Line Current Distortion in Single-Phase Vienna Rectifiers Using Model-Based Predictive Control," in *Energies*, vol. 11, no. 5, pp. 1-22, May 2018.

# Chapter 2

# Inductance-Independent Control for Continuous and Discontinuous Current Mode

### 2.1 Introduction

The previous chapter described the vital role of power converters in the solar power systems. The minimization of passive components in power converters not only solves many space issue for hardware designer, but also gives many advantages such as, e.g. cost reduction. In this thesis, the inductance-independent CCM&DCM control method is proposed to reduce the inductor volume at certain switching frequency.

In this chapter, first, the inductor minimization by the CCM&DCM control method is explained in detail. Then, the state-of-the-art CCM&DCM control methods are reviewed and discussed. The control loop gain

characteristics of the CCM and DCM operations are completely different from each other, leading to the requirement of the separation for the CCM and DCM duty generations in the CCM&DCM control methods. Therefore, the CCM&DCM control methods are basically combined three parts;

- (i) CCM control,

- (ii) DCM control,

- (iii) Current mode detection of CCM and DCM.

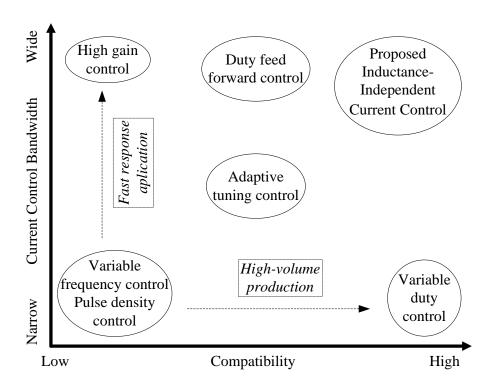

The DCM control methods and the current mode detection of CCM and DCM in each parts are discussed and the advantages/disadvantages in term of control performance and compatibility are elaborately demonstrated. A comparison chart is provided to discuss about the most applicable CCM&DCM control method for the solar power system.

Then, the proposed inductance-independent CCM&DCM control method is described in detail. The beneficial position of the proposed control method along with other conventional control methods is presented. The superiority position of proposed converter is discussed to show the contribution of this research.

# 2.2 Inductor Minimization with CCM&DCM Control Method

In this chapter, the typical boost converter in the single-phase PV system is considered as an example.

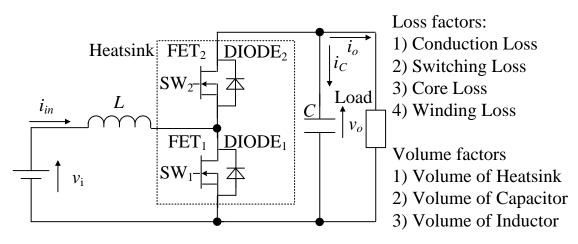

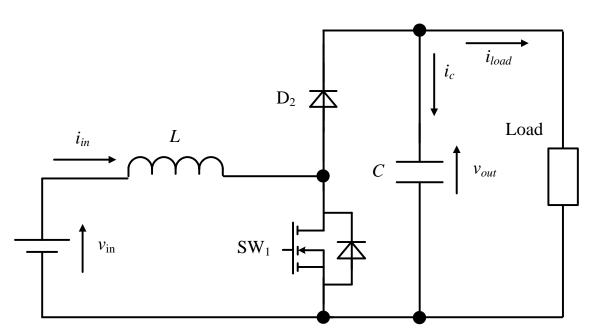

Fig. 2.1 depicts the typical boost converter in the single-phase PV system. As shown in Fig. 1.6 and Fig. 2.1, there are three factors which contribute to the volume; the heatsink of the semiconductor devices  $Vol_H$ , the boost inductor  $Vol_L$  and the capacitor  $Vol_C$ . The capacitor volume is determined by the capacitance, the allowable current ripple and the capacitor type. In the single-phase PV system, the factor dominating the design of the capacitor volume is the capacitance, which is designed to absorb the power ripple from the single-phase grid, i.e. the passive power decoupling [2-1]. Active power decoupling methods can reduce the required capacitance, leading to the capacitor volume reduction. However, the topic on the active power decoupling methods is out of scope of this thesis. Hence, the volumereducible components in the typical boost converter is the inductor and the heatsink.

The volume of the heatsink changes according to the loss from the

Fig. 2.1. Typical boost converter. The losses and volume is calculated in order to design the power density and the power conversion efficiency.

semiconductor devices. The estimation of the heatsink volume  $Vol_H$  is conducted based on the Cooling System Performance Index (CSPI) [2-2], which is defined as the inverse factor of the thermal resistance per unit volume; hence, the higher CSPI becomes, the more effective the heat is dissipated through the heatsink,

where  $R_{th(s-a)}$  is the required thermal resistance between the heatsink and the ambience,  $T_j$  is the junction temperature of the MOSFET,  $T_a$  is the ambient temperature,  $R_{th(j-s)}$  is the thermal resistance between the junction and the heatsink,  $P_{cond}$  and  $P_{sw}$  are the conduction loss and switching loss of the semiconductor devices.

Meanwhile, the inductor volume  $Vol_L$  is calculated by the Area Product [2-3]-[2-4],

$$Vol_{L} = K_{V} \left( \frac{LI_{\max}^{2}}{K_{u}B_{\max}J} \right)^{\frac{3}{4}} = K_{V} \left[ \frac{V_{i}(V_{o} - V_{i})I_{avg}}{2K_{u}B_{\max}JV_{o}} \frac{1}{f_{sw}} \left( \sqrt{\Delta I} + \frac{1}{\sqrt{\Delta I}} \right) \right]^{\frac{3}{4}} (2.2)$$

where  $K_V$  is the coefficient which depends on the shape of the core [2-3],  $K_u$ is the window utilization factor,  $B_{max}$  is the maximum flux density of the core, J is the current density,  $\Delta I$  is the boost inductor current ripple,  $f_{sw}$  is the switching frequency. It is clearly understood from (2.2) that, the inductor volume depends on both the switching frequency  $f_{sw}$  and the current ripple  $\Delta I$ . In the typical inductor minimization method, the inductor current ripple is designed to be smaller than 10%, whereas the switching frequency  $f_{sw}$  is increased. Nevertheless, the high switching frequency  $f_{sw}$  leads to the increase in the switching loss, requiring the larger heatsink as aforementioned. There are several methods to avoid the increase in the switching loss even with the high switching frequency, e.g. the multi-level topology [2-5]-[2-6] or the soft switching technique [2-7]-[2-10]. The multilevel topology enables the low switching frequency of the low voltage rating switching devices in each modular to result in the high current-ripple equivalent-frequency. In the other words, the multi-level topology can minimize the inductor without increasing the heatsink volume. However, the voltage unbalance issue is one of the main problems restricting the application of the multi-level topology. On the other hand, soft switching techniques can greatly reduce the switching loss, in which resonance between an inductor and a capacitor is utilized in order to achieve zerovoltage switching (ZVS). However, in order to satisfy conditions for ZVS, these methods suffer many drawbacks such as, e.g. a requirement of additional components, a restriction of controllable duty ratio or a sharp decrease in the efficiency at light load.

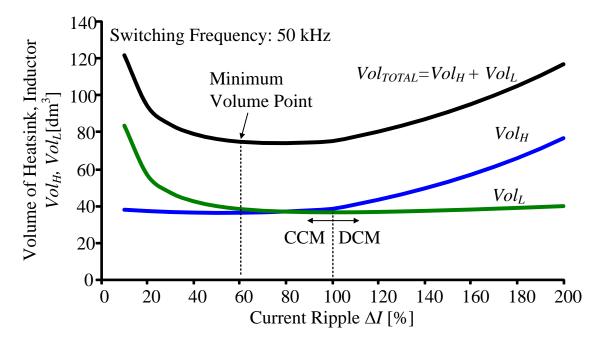

Fig. 2.2 shows the relationship among the current ripple, the inductor volume and the heatsink volume [2-4]. This thesis focuses on the minimization limitation of the inductor volume at certain switching frequency by varying the current ripple. Focusing on the characteristic of the inductor volume, the minimization of the inductor volume by the high current ripple design shows a high effectiveness in the current ripple range from 10% to around 40%, showing by the sharp decrease slope of the inductor volume. However, the high current ripple design becomes less

Fig. 2.2. Relationship among current ripple, inductor volume and heatsink volume. By varying the current ripple, the smallest total volume of the inductor and the heatsink is achieved at the current ripple of 60%.

effective on the inductor volume minimization when the current ripple keeps increasing from 40%. Especially, the high current ripple has no effectiveness on the inductor volume minimization when the current ripple is higher than 100%, where is the boundary between the CCM and DCM operations. It implies that the design which makes the circuit deeply operate in DCM provides no benefit on the inductor minimization.

Meanwhile, the high current ripple design increases the root-meansquare current value even with the same current average value, i.e. same output power, leading to the increase in the conduction loss of the semiconductor devices. As aforementioned, the high conduction loss of the switching devices requires the larger heatsink. Therefore, it is clearly observed from Fig. 2.2 that the heatsink volume increases with the high current ripple design. It implies that there is the minimum total volume of the inductor and the heatsink as the current ripple is varied. The design of the typical boost converter in [2-4] confirms the minimum total voltage of the inductor and the heatsink is achieved with the current ripple of 60%, leading to the CCM operating at rated load and the DCM operation at light load, i.e. the mixed conduction mode between CCM and DCM. Therefore, this thesis focuses on the CCM&DCM control methods to achieve the inductor minimization.

## 2.3 Overview of Continuous and Discontinuous Current Mode Control

Fig. 2.3 depicts the classification of the CCM&DCM control methods. In the unidirectional converter such as, e.g. one-switch boost converters or bridgeless power factor converters (PFC), the DCM operation inevitably occurs at light load [2-11]-[2-28]. On the other hand, in the bidirectional converters such as, e.g. two-switch boost converters or grid-tied inverter, the occurrence of DCM is difficult to analyze because the DCM operation occurs only during the dead time interval near the current zero crossing points [2-29]-[2-37]. In order to deal with the nonlinearity in DCM, the separation for the CCM and DCM duty generations is required in the CCM&DCM control methods. Hence, the CCM&DCM control methods intrinsically need the current mode detection of CCM and DCM. Consequently, the CCM&DCM control methods are basically combined three parts; CCM control, DCM control, the current mode detection of CCM and DCM. The CCM control methods are divided into two groups: CCM feedforward control and CCM feedback control, which are not the main focus on this thesis. Therefore, the explanation of the CCM control methods are omitted.

Fig. 2.3. Classification of CCM&DCM control methods.

On the other hand, the conventional DCM control methods can be divided into two groups: DCM feedforward control and DCM feedback control. The DCM feedforward control is divided into three subgroups: variable duty control [2-11]-[2-18], variable frequency control [2-19]-[2-20], pulse density control (or bang-bang control) [2-21]-[2-23] and adaptive tuning control [2-24]. Meanwhile, the DCM feedback control are classified into four subgroups: high gain control [2-25]-[2-26], and duty feedforward control [2-27]-[2-31]. The current mode detection of CCM and DCM can be divided into three groups: zero current detection [2-23]-[2-24], [2-26], comparison of current relationship [2-14] and comparison of duty relationship [2-27]-[2-28], [2-31]. The combination of the CCM control, the DCM control and the current mode detection in Fig. 2.3 results in the CCM&DCM control. For instance, the CCM&DCM control in [2-23] is combined of the CCM feedforward control, the DCM feed forward control (i.e. the pulse density control), and the current mode detection of CCM and DCM (i.e. the zero current detection).

# 2.4 Conventional Discontinuous Current Mode Control

#### 2.4.1 DCM Feedforward Control

The feedforward current control is generally applied to control the DCM current, because there is nonlinearities in DCM, which restricts the application of the feedback control [2-38]. The feedforward current control benefits from the simple controller design, and the elimination of the current sensor. Nevertheless, the feedforward current control alone cannot provide the accurate current control in the practical application due to several reasons such as, e.g. the tolerance of the devices, or the temperature-dependent value variation. Therefore, the feedforward current control for CCM and DCM are generally employed with an outer loop voltage feedback control, resulting in a cascade control [2-39]. The error between the current reference and the actual current is compensated by the outer loop voltage feedback control. This cascade control for CCM and DCM is basically divided into three subgroups: variable duty control [2-11]-[2-18], variable frequency control [2-19]-[2-20], pulse density control (or bang-bang control) [2-21]-[2-23] and adaptive tuning control [2-24].

#### (1) Variable duty control

The duty in the DCM operation directly depends on the current due to the nonlinearity [2-38]. Consequently, the variable duty control achieves the current regulation by varying the duty under the constant switching frequency, i.e. pulse width modulation (PWM). The relationship between the duty and the current in DCM is based on the reduced-order model or the fullorder model. This variable duty control for DCM is employed in numerous applications such as, e.g. bidirectional DC/DC converters, single-phase gridtied inverters, three-phase single-switch inverters, or the VIENNA rectifiers [2-11]-[2-18].

Fig. 2.4 depicts the variable duty control system for DCM in DC/DC converter [2-13]. The DC/DC converter is designed to operate under only DCM at rate load of 45 kW. The duty controlling the switching devices is calculated directed from the inductance, the switching frequency, the inductor current and the input/output voltage (cf., equation (1) of [2-3]). This control method for DCM can be simply implemented in the existing controller. However, unlike DCM, the CCM operation does not exhibit the nonlinearity between the current and the duty. In other words, the current in

CCM does not depend on the duty, but only depends on the change of the duty. Due to this difference between the controls of two current modes, it is difficult to design a fixed high bandwidth control for the converter operating in both CCM and DCM. Hence, the variable current control for DCM is usually employed into the converters operating under only DCM. Another drawback of the variable duty feedforward control is the dependence of the inductance, which is shown in Fig. 2.4.

The example of the control method for the boost converter operating in

Variable duty control system for DCM (cf. equation (1) of [2-3])

Fig. 2.4. Variable duty control system for DCM in DC/DC converter.

both CCM and DCM can be found in [2-14]. In particular, the CCM current feedback control is employed with the variable duty feedforward control for DCM. As mentioned above, due to the difference of the characteristic between the CCM current feedback control and the DCM variable duty feedforward control, the bandwidth of the mixed control loop is necessary to be low to ensure the control stability, e.g. 100 Hz to 1 kHz despite the sampling frequency of 10 kHz [2-14].

#### (2) Variable frequency control

Fig. 2.5 depicts the variable frequency control system for DCM in DC/AC converter. The principle of this DCM variable frequency control method is similar to that of the DCM variable duty control method; due to the DCM nonlinearity, the DCM current depends directly to the duty, and the switching frequency. Therefore, in the variable frequency control, the switching frequency is varied whereas the off-time (or on-time) is kept constant to achieve the current regulation, resulting in pulse frequency modulation (PFM) [2-19]-[2-20]. Compared to the variable duty control (PWM), the variable frequency control (PFM) spreads the switching-frequency harmonic components over a wide range of frequency, which

Fig. 2.5. Variable frequency control system for DCM in DC/AC converter.

enables the minimization of the filter. Nevertheless, the DCM variable frequency control still suffers the similar drawbacks of the DCM variable duty control, which are the difficulty in control both CCM and DCM, and the inductance dependence. Hence, the variable frequency control for DCM is usually employed into the converters operating under only DCM with low current control bandwidth.

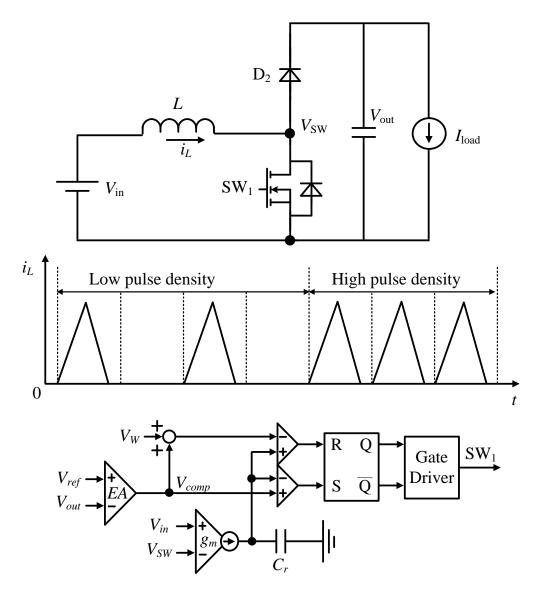

### (3) Pulse density control

Fig. 2.6 depicts the pulse density control system for DCM in DC/DC converter. In the pulse density control, each DCM interval is treated as one pulse; the density of the pulses is modulated in order to achieve the current regulation, resulting in pulse density modulation (PDM) [2-21]-[2-23]. The

Fig. 2.6. Pulse density control system for DCM in DC/DC converter.

literature in [2-21]-[2-23] proposed the pulse density control for buck converters. The output voltage is compared with the voltage reference to determine the pulse density. Apart from the similar drawbacks of the DCM variable duty control, the pulse density control has some critical drawbacks; the control stability is difficult to be evaluated. Therefore, the pulse density control is normally applied into low power application.

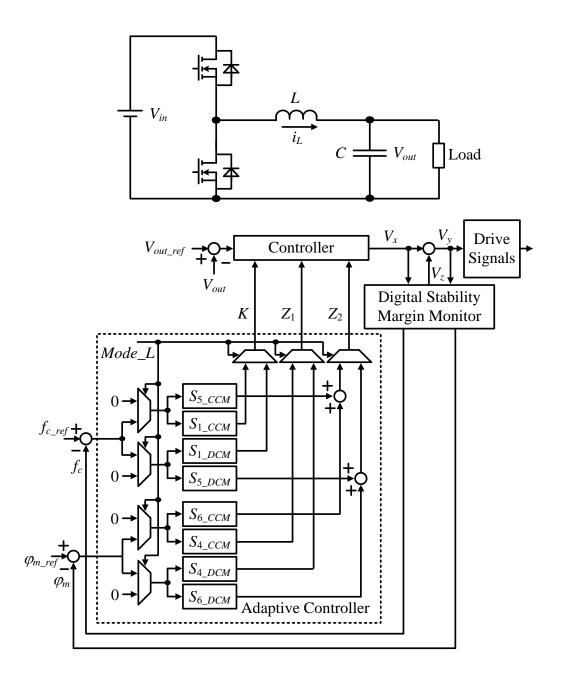

#### (4) Adaptive tuning control

Fig. 2.7 depicts the adaptive tuning control system for DCM in DC/DC converter. As another approach to control both CCM and DCM, a method of continuous adaptive tuning of voltage-mode digital controllers has been proposed in [2-24]. The adaptive controller is designed based on the small-signal model of CCM and DCM. When the DCM operation is detected, the tuning system operates by updating the DCM control gain, and the DCM control coefficients in order to zero the error between the desired and measured stability margins. Simultaneously, the inputs to the CCM control part are held at zero such that the CCM compensator parameters remain unchanged. In reverse, when the CCM operation is detected, the CCM compensator are tuned and loaded into the controller, whiles the most recent

Fig. 2.7. Adaptive tuning control system for DCM in DC/DC converter.

DCM compensator parameters are stored. Note that the current mode determination is carried out by comparing the switched-mode voltage to zero (ground). This detection method assumes that during the zero current interval in DCM, the switched-mode voltage is clamped at the output voltage; however, in practical application, the switched-mode voltage oscillates during the zero current interval due to the energy oscillation between the inductor and the parasitic capacitance of the switches, which becomes more severe with a low inductance and a high switching frequency. Consequently, the current mode determination in [2-24] has to be tuned for each individual prototype to obtain the desired operation.

### 2.4.2 DCM Feedback Control

In the DCM operation, the duty-to-current loop gain becomes significantly low at light load compared to that in the CCM operation. Therefore, many control methods have been proposed to deal with this load-dependent loop-gain decrease. The outer loop voltage feedback control becomes optional with the employment of the current feedback control. In particular, the feedback current control for CCM&DCM is basically divided into four subgroups: high gain control [2-25]-[2-26], and duty feedforward control [2-27]-[2-31].

#### (1) High gain control

The principle of the high gain control for the DCM operation is to use a high-gain controller to deal with the load-dependent loop gain decrease at light load in DCM. In [2-25], a controller with the cutoff frequency of 20 kHz is employed to control the current with the frequency of just 50 Hz. The obvious drawback of the high gain control is the requirement of the high sampling frequency to implement the high gain controller. In addition, when the converters are designed to operate in both CCM and DCM, two different controllers are required because there is no load-dependent loop gain

decrease in CCM [2-26]. Furthermore, the current mode determination is also necessary to choose the controller for corresponding current mode. In [2-26], the current mode determination is accomplished by the detection of the zero current in DCM. However, the zero current detection faces many challenges in practical applications, one of which is the current oscillation during the zero-current interval. In particular, this current oscillation is caused by the energy oscillation between the inductor and the parasitic capacitance of the switches, which becomes more severe with a low inductance and a high switching frequency. Consequently, the current mode determination in [2-26] has to be tuned for each individual prototype to obtain the desired operation.

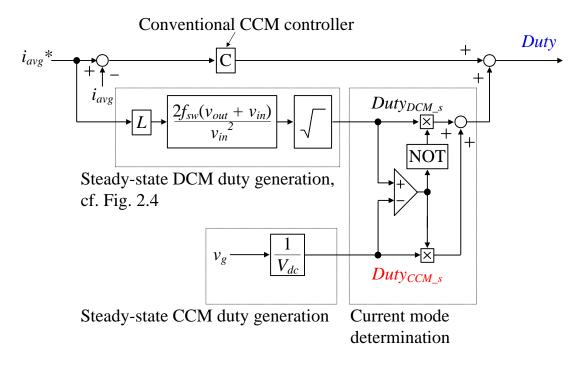

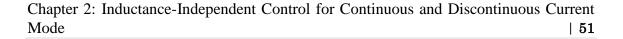

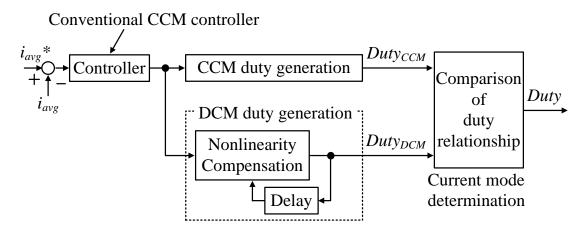

#### (2) Duty feedforward control

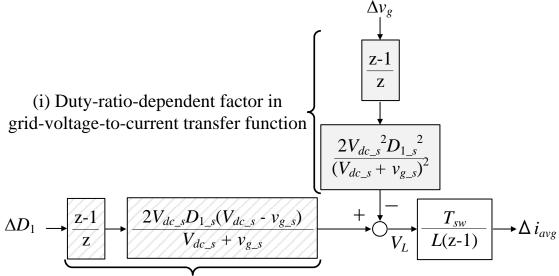

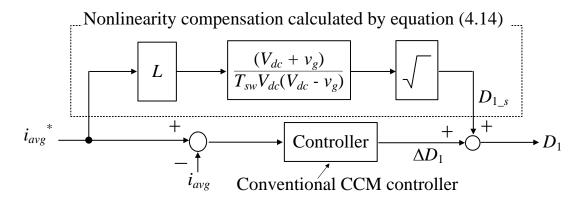

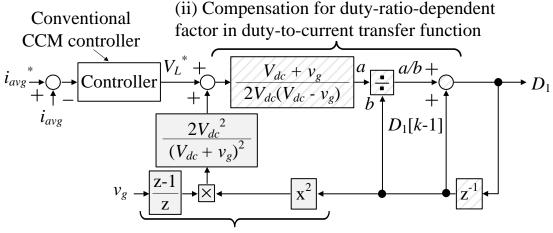

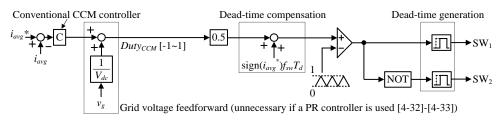

Fig. 2.8 depicts the duty feedforward control for the boost converter operation in both CCM and DCM [2-27]. The duty feedforward control might appear differently for a variety of application such as, e.g. boost converters [2-27]-[2-28], Vienna rectifiers [2-29], [2-31], or three-phase buck-type rectifier [2-30]. Nevertheless, the same principle to control both CCM and DCM is applied in these duty feedforward control methods. In the

Fig. 2.8. Duty feedforward control for boost converter operation in both CCM and DCM.

only-CCM control, the steady-state CCM duty is fed forward to the output of the controller; consequently, the controller handles only the small difference of the duty between two consecutive sampling periods. This implies that the controllers with low gain is sufficient. The same control mechanism can be applied in order to control the DCM current with lowgain controllers. As shown in Fig. 2.5, in the only-DCM control, the steadystate DCM duty is fed forward to the output of the controller. Furthermore, in order to avoid the current mode determination by the zero current detection, the current mode is determined by the comparison of the steadystate duty between CCM and DCM. Nevertheless, the duty feedforward control still suffers the drawback as the inductance dependence in the steadystate DCM duty generation, which makes the control stability sensitive to the circuit parameter.

### 2.4.3 Problems of Inductance-Dependent Control Systems